I’m trying to read a word document using C#. I am able to get all text but I want to be able to read line by line and store in a list and bind to a gridview. Currently my code returns a list of one item only with all text (not line by line as desired). I’m using the Microsoft.Office.Interop.Word library to read the file. Below is my code till now:

Application word = new Application();

Document doc = new Document();

object fileName = path;

// Define an object to pass to the API for missing parameters

object missing = System.Type.Missing;

doc = word.Documents.Open(ref fileName,

ref missing, ref missing, ref missing, ref missing,

ref missing, ref missing, ref missing, ref missing,

ref missing, ref missing, ref missing, ref missing,

ref missing, ref missing, ref missing);

String read = string.Empty;

List<string> data = new List<string>();

foreach (Range tmpRange in doc.StoryRanges)

{

//read += tmpRange.Text + "<br>";

data.Add(tmpRange.Text);

}

((_Document)doc).Close();

((_Application)word).Quit();

GridView1.DataSource = data;

GridView1.DataBind();

Dynamic Random Access Memory ( DRAM ) or the half-German term dynamic RAM describes a technology for an electronic memory component with random access ( Random-Access Memory , RAM), which is mainly used in computers , but also in other electronic devices such as printers is used. The storing element is a capacitor that is either charged or discharged. It is accessible via a switching transistor and either read out or written with new content.

The memory content is volatile, i.e. the stored information is lost if there is no operating voltage or if it is refreshed too late.

introduction

A characteristic of DRAM is the combination of a very high data density combined with very inexpensive manufacturing costs. It is therefore mainly used where large amounts of memory have to be made available with medium access times (compared to static RAM , SRAM).

In contrast to SRAMs, the memory content of DRAMs must be refreshed cyclically (refresh). This is usually required every tens of milliseconds . The memory is refreshed line by line. For this purpose, a memory line is transferred in one step to a line buffer located on the chip and from there is written back to the memory line in an amplified manner. Hence the term «dynamic» comes from. In contrast, with static memories such as SRAM, all signals can be stopped without loss of data. Refreshing the DRAM also consumes a certain amount of energy in the idle state. SRAM is therefore preferred in applications where a low quiescent current is important.

Charge in the storage cell capacitors evaporates within milliseconds, but due to manufacturing tolerances, it can persist in the storage cells for seconds to minutes. Researchers at Princeton University managed to forensically read data immediately after a cold start. To be on the safe side , the components are always specified with the guaranteed worst-case value , i.e. the shortest possible holding time.

Storage manufacturers are continuously trying to reduce energy consumption by minimizing losses due to recharging and leakage currents. Both depend on the supply voltage, which for DDR2-SDRAM is 1.8 volts, while DDR-SDRAM is still supplied with 2.5 volts. In the DDR3 SDRAM introduced in 2007 , the voltage was lowered to 1.5 volts.

A DRAM is designed either as an independent integrated circuit or as a memory cell part of a larger chip.

The «random» in random access memory stands for random access to the memory content or the individual memory cells, as opposed to sequential access such as, for example, with FIFO or LIFO memories (organized on the hardware side) .

construction

A DRAM does not consist of a single two-dimensional matrix, as shown in simplified form in the article semiconductor memory . Instead, the memory cells , which on the surface of this are arranged and wired, divided into a sophisticated hierarchical structure. While the internal structure is manufacturer-specific, the logical structure visible from the outside is standardized by the JEDEC industrial committee . This ensures that chips from different manufacturers and of different sizes can always be addressed according to the same scheme.

Structure of a memory cell

The structure of a single DRAM memory cell is very simple, it only consists of a capacitor and a transistor . Today a MOS field effect transistor is used . The information is stored as an electrical charge in the capacitor. Each memory cell stores one bit . While planar capacitors were mostly used in the past, two other technologies are currently used:

- In the stack technology (English stack , Stack ‘ ) of the capacitor is built up across the transistor.

- In the trench technology (English trench , trench ‘ ), the capacitor by etching a 5-10 micron hole (or trench) deep generated in the substrate.

- Schematic structure of the basic technologies for DRAM cells (cross-sections)

-

Planar technology

-

Stacking technology

-

Trench technology with poly-Si plate

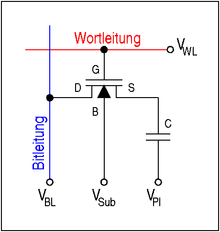

Basic structure of a memory cell from a transistor and a capacitor (1T1C cell)

The upper connection shown in the adjacent figure is either charged to the bit line voltage V BL or discharged (0 V). The lower connection of all capacitors is connected together to a voltage source, which ideally has a voltage of V Pl = 1/2 · V BL . This allows the maximum field strength in the dielectric of the capacitor to be halved.

The transistor (also called the selection transistor) serves as a switch for reading and writing the information from the cell. For this purpose, via the word line (English word line a positive voltage) to the gate terminal «G» of the n-MOS transistor V WL applied. Characterized a conductive connection between the source ( «S») and the drain regions is ( «D») was prepared which the cell capacitor to the bit line (English bitline connects). The substrate connection “B” ( bulk ) of the transistor is connected either to the ground potential or to a slightly negative voltage V Sub to suppress leakage currents.

Due to their very simple structure, the memory cells require very little chip area. The design-related size of a memory cell is often given as the multiple of the square area F² of the smallest feasible structure length (“ minimum feature size ” or F for short): A DRAM cell today requires 6 or 8 F², while an SRAM cell requires more than 100 F² . Therefore, a DRAM can store a much larger number of bits for a given chip size. This results in much lower manufacturing costs per bit than with SRAM . Among the types of electronic memory commonly used today, only the NAND flash has a smaller memory cell with around 4.5 F² (or 2.2 F² per bit for multilevel cells).

Structure of a memory line («Page»)

Interconnection of several memory cells to form a memory line

Further by connecting the memory cells to a word line to obtain a memory line , commonly referred to as side (English page ) is referred to. The characteristic of a row is the property that when a word line (shown in red) is activated, all the associated cells simultaneously output their stored content to the bit line assigned to them (shown in blue). A common page size is 1 Ki , 2 Ki, 4 Ki (…) cells.

Structure of a cell field

Two-dimensional interconnection of memory cells to form a cell field

The memory cells are interconnected in a matrix arrangement: ‘word lines’ connect all control electrodes of the selection transistors in a row, bit lines connect all drain regions of the selection transistors in a column.

At the lower edge of the matrix, the bit lines are connected to the (primary) read / write amplifiers ( sense amplifiers ). Because they have to fit into the tight grid of the cell array, they are two negative feedback in the simplest form CMOS — inverter composed of only four transistors. Their supply voltage is just equal to the bit line voltage V BL . In addition to their function as an amplifier of the read out cell signal, they also have the side effect that their structure corresponds to that of a simple static memory ( latch ) . The primary sense amplifier thus simultaneously serves as a memory for a complete memory line.

The switches shown above the sense amplifiers are used in the inactive state to precharge the bit lines to a level of ½ · V BL , which just represents the mean value of the voltage of a charged and a discharged cell.

A large number of these memory matrices are interconnected on a memory chip to form a coherent memory area, so the chip is internally divided into submatrices (transparent to the outside). Depending on the design, all data lines are routed to a single data pin or distributed over 4, 8, 16 or 32 data pins. This is then the data width k of the individual DRAM chip; several chips must be combined for wider bus widths.

Address decoding

Basic structure of the row and column address decoding for a cell field

The adjacent diagram shows the basic structure of the address decoding for a single cell field. The row address is fed to the row decoder via n address lines . This selects exactly one from the 2 n word lines connected to it and activates it by raising its potential to the word line voltage V WL . The memory row activated as a result in the cell array now outputs its data content to the bit lines. The resulting signal is amplified, stored and at the same time written back to the cell by the (primary) sense amplifiers.

The decoding of the column address and the selection of the data to be read is a two-step process. In a first step, the m address lines of the column address are fed to the column decoder . This selects one of the column selection lines usually connected 2 m and activates them. In this way — depending on the width of the memory — k bit lines are selected simultaneously. In a second step, in the column selection block, this subset of k bit lines from the total of k * 2 m bit lines is connected to the k data lines in the direction of the outside world. These are then amplified by a further read / write amplifier (not shown).

In order to limit the crosstalk between neighboring memory cells and their leads, the addresses are usually scrambled during decoding , namely according to a standardized rule so that they cannot be found in the order of their binary significance in the physical arrangement.

Internal processes

Initial state

- In the idle state of a DRAM, the word line is at low potential ( U WL = 0 V). As a result, the cell transistors are non-conductive and the charge stored in the capacitors remains — apart from undesired leakage currents.

- Both switches sketched in the diagram of the cell field above the sense amplifiers are closed. They keep the two bit lines, which are jointly connected to a sense amplifier, at the same potential (½ * U BL ).

- The voltage supply to the read amplifier ( U BL ) is switched off.

Activation of a memory line

- From the bank and line address transferred with an Activate (see diagrams for «Burst Read» access) it is first determined in which bank and, if applicable, in which memory block the specified line is located.

- The switches for the ‘bit line precharge’ are opened. The bit lines that have been charged up to half the bit line voltage are thus decoupled from each voltage source.

- A positive voltage is applied to the word line. The transistors of the cell array thus become conductive. Due to the long word lines, this process can take several nanoseconds and is therefore one of the reasons for the «slowness» of a DRAM.

- A charge exchange takes place between the cell capacitor and one of the two bit lines connected to a sense amplifier. At the end of the charge exchange, the cell and bit line have a voltage of

-

- charged. The sign of the voltage change (±) depends on whether a ‘1’ or a ‘0’ was previously stored in the cell. Due to the high bit line capacitance C BL / C = 5… 10 (due to the line length), the voltage change is only 100 mV. This reloading process also takes a few nanoseconds due to the high bit line capacitance.

- Towards the end of this recharging process, the supply voltage ( U BL ) of the primary read amplifier is switched on. These begin by amplifying the small voltage difference between the two bit lines and charge one of them to U BL and discharge the other to 0 V.

Reading data

- To read data, the column address must now be decoded by the column decoder.

- The column select line (CSL) corresponding to the column address is activated and connects one or more bit lines at the output of the primary sense amplifier to data lines which lead out of the cell array. Due to the length of these data lines, the data at the edge of the cell field must be amplified again with a (secondary) sense amplifier.

- The data read out are read parallel into a shift register, where with the external clock (English clock synchronized) and amplified output.

Writing of data

- The data to be written into the DRAM are read in almost simultaneously with the column address.

- The column address is decoded by the column decoder and the corresponding column selection line is activated. This re-establishes the connection between a data line and a bit line.

- In parallel with the decoding of the column address, the write data arrive at the column selection block and are passed on to the bit lines. The (weak) primary sense amplifiers are overwritten and now assume a state that corresponds to the write data.

- The sense amplifiers now support the reloading of the bit lines and the storage capacitors in the cell array.

Deactivation of a memory line

- The word line voltage is reduced to 0 V or a slightly negative value. This makes the cell transistors non-conductive and decouples the cell capacitors from the bit lines.

- The power supply to the sense amplifiers can now be switched off.

- The bit line precharge switches connecting the two bit lines are closed. The initial state (U = ½ U BL ) is thus restored on the bit lines .

Timing parameters of the internal processes

Definition of the timing parameters t RCD and CL

NB, memory bars are often marked with a number set in the form of CL12-34-56 , the first number standing for the CL , the second for t RCD , the third for t RP ; an occasionally appended fourth pair of digits denotes t RAS . This number set is also referred to as (CL) (tRCD) (tRP) (tRAS) .

t RCD

The parameter t RCD ( RAS-to-CAS delay , row-to-column delay ) describes the time for a DRAM, which (after the activation of a word line activate ) must have elapsed before a read command ( read ) shall be sent. The parameter is due to the fact that the amplification of the bit line voltage and the writing back of the cell content must be completed before the bit lines can be further connected to the data lines.

CL

The parameter CL ( CAS latency , also t CL ) describes the time that passes between the sending of a read command and the receipt of the data.

See also: Column Address Strobe Latency

t RAS

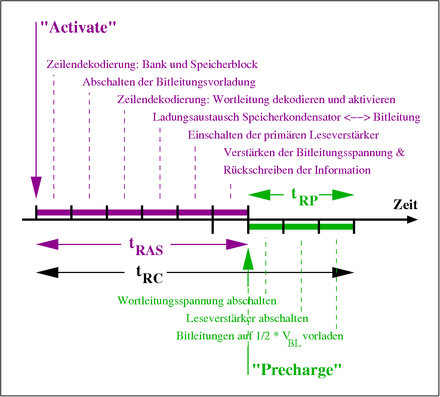

Definition of the timing parameters t RAS , t RP and t RC

The parameter t RAS ( RAS pulse width , Active Command Period , Bank Active Time ) describes the time that must have elapsed after activating a line (or a line in a bank) before a command to deactivate the line ( precharge , Closing the bank) may be sent. The parameter is given by the fact that the amplification of the bit line voltage and the writing back of the information into the cell must be completely completed before the word line can be deactivated. d. H. the smaller the better.

t RP

The parameter “ t RP ” ( “Row Precharge Time” ) describes the minimum time that must have elapsed after a precharge command before a new command to activate a line in the same bank can be sent. This time is defined by the condition that all voltages in the cell field (word line voltage, supply voltage of the sense amplifier) are switched off and the voltages of all lines (especially those of the bit lines) have returned to their starting level.

t RC

The parameter «t RC « ( «Row Cycle Time» ) describes the length of time that must have elapsed between two successive activations of any two rows in the same bank . The value largely corresponds to the sum of the parameters t RAS and t RP and thus describes the minimum time required to refresh a memory line.

DRAM-specific properties

Address multiplex

addressing

The address lines of a DRAM are usually multiplexed , whereas with SRAMs the complete address bus is usually routed to pins for the purpose of higher speed, so that access can take place in a single operation.

Asynchronous DRAMs ( EDO, FPM ) have two input pins RAS ( Row Address Select / Strobe ) and CAS ( Column Address Select / Strobe ) to define the use of the address lines: if there is a falling edge from RAS, the address on the address lines is displayed as Row address interpreted, with a falling edge from CAS it is interpreted as a column address.

RAS

Row Address Strobe , this control signal is present during a valid row address. The memory module stores this address in a buffer.

CAS

Column Address Select or Column Address Strobe , this control signal is present during a valid column address . The memory module stores this address in a buffer.

Synchronous DRAMs ( SDRAM , DDR-SDRAM ) also have the control inputs RAS and CAS , but here they have lost their immediate function. Instead, with synchronous DRAMs, the combination of all control signals ( CKE , RAS , CAS , WE , CS ) are evaluated with a rising clock edge in order to decide whether and in what form the signals on the address lines must be interpreted.

The advantage of saving external address lines is offset by an apparent disadvantage in the form of delayed availability of the column address. However, the column address is only required after the row address has been decoded, a word line has been activated and the bit line signal has been evaluated. However, this internal process requires approx. 15 ns, so that the column address received with a delay does not have a negative effect.

Burst

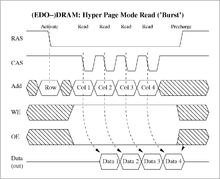

|

‘Burst Read’ of an asynchronous (EDO) DRAM. The associated column address ( Col ) had to be specified for each burst bit . |

‘Burst Read’ of a synchronous (SDR) DRAM |

|

Cell array of a DRAM with primary sense amplifiers (below) |

A DRAM read amplifier is constructed analogously to the transistors M1, M2, M3 and M4 of such a 6-transistor SRAM cell |

The images on the right show read access in the so-called burst mode for an asynchronous and a synchronous DRAM , as is used with the BEDO DRAM . The characteristic element of a burst access (when reading or writing) is the immediate succession of the data (Data1,…, Data4). The data belong to the same row of the cell field and therefore have the same row address (English row ) but different column addresses (Col1, …, Col4). The time required for the provision of the next data bit within the burst is very short compared to the time required for the provision of the first data bit, measured from the activation of the line.

While all column addresses within the burst had to be specified for asynchronous DRAMs (Col1, …, Col4), only the start address is specified for synchronous DRAMs (SDR, DDR). The column addresses required for the rest of the burst are then generated by an internal counter.

The high data rate within a burst is explained by the fact that the read amplifier only needs to be read (or written) within a burst. The sense amplifiers made up of 2 CMOS inverters (4 transistors) correspond to the basic structure of the cell of a static RAM (see adjacent diagrams). To provide the next burst data bit, only the column address needs to be decoded and the corresponding column selection line activated (this corresponds to the connection lines to the gate connection of the transistors M5 and M6 of an SRAM cell).

Refresh

The refreshment of the memory content , which is necessary at short time intervals , is generally referred to by the English term refresh . The necessity arises from the occurrence of undesired leakage currents which change the amount of charge stored in the capacitors. The leakage currents have an exponential temperature dependency: The time after which the content of a memory cell can no longer be correctly assessed ( retention time ) is halved with a temperature increase of 15 to 20 K. Commercially available DRAMs usually have a prescribed refresh period of 32 ms or 64 ms.

Technically, the primary sense amplifiers in the memory chip (see figure above) are equipped with the function of a latch register. They are designed as SRAM cells, i.e. as flip-flops . When a certain row (English page , Ger. Page ) is selected, the entire line is copied into the latches of the sense amplifier. Since the outputs of the amplifier are also connected to its inputs at the same time, the amplified signals are written back directly into the dynamic memory cells of the selected row and are thus refreshed.

There are different methods of this refresh control:

- RAS-only refresh

- This method is based on the fact that activating a row is automatically linked to an evaluation and writing back of the cell content. For this purpose, the memory controller must externally apply the line address of the line to be refreshed and activate the line via the control signals (see diagram for RAS-only refresh with EDO-DRAM ).

- CAS before RAS refresh

- This refresh method got its name from the control of asynchronous DRAMs, but has also been retained with synchronous DRAMs under the name Auto-Refresh . The naming was based on the otherwise impermissible signal sequence — this type of signal setting is avoided in digital technology because it is relatively error-prone (e.g. during synchronization) — that a falling CAS edge was generated before a falling RAS edge ( see diagram for CBR refresh with EDO-DRAM ). In response to the signal sequence, the DRAM performed a refresh cycle without having to rely on an external address. Instead, the address of the line to be refreshed was provided in an internal counter and automatically increased after the execution.

- Self-refresh

- This method was introduced for special designs of asynchronous DRAMs and was only implemented in a binding manner with synchronous DRAMs. With this method, external control or address signals (for the refresh) are largely dispensed with (see diagram for self-refresh with EDO-DRAM ). The DRAM is in a power-down mode , in which it does not react to external signals (an exception are of course the signals that indicate that it is remaining in the power-saving mode). To obtain the stored information, a DRAM-internal counter is used, which initiates an auto-refresh ( CAS-before-RAS-Refresh ) at predetermined time intervals . In recent DRAMs (DDR-2, DDR-3), the period for the refresh is controlled mostly dependent on the temperature (a so-called T emperature C ontrolled S eleven R efresh, TCSR), in order to reduce the operating current in the self-refresh at low temperatures.

Depending on the circuit environment, normal operation must be interrupted for the refresh; for example, the refresh can be triggered in a regularly called interrupt routine. For example, it can simply read any memory cell in the respective line with its own counting variable and thus refresh this line. On the other hand, there are also situations (especially in video memories) in which the entire memory area is addressed at short intervals anyway, so that no separate refresh operation is required. Some microprocessors , such as the Z80 or the latest processor chipsets , do the refresh fully automatically.

Bank

Before the introduction of synchronous DRAMs, a memory controller had to wait until the information of an activated row was written back and the associated word line was deactivated. Only exactly one line could be activated in the DRAM at a time. Since the length of a complete write or read cycle ( row cycle time, t RC ) was around 80 ns, access to data from different rows was quite time-consuming.

With the introduction of synchronous DRAMs, 2 (16 MiB SDRAM), then 4 (64 MiB SDRAM, DDR-SDRAM), 8 (DDR-3-SDRAM) or even 16 and 32 ( RDRAM ) memory banks were introduced. Memory banks are characterized by the fact that they each have their own address registers and sense amplifiers, so that one row could now be activated per bank . By operating several banks at the same time, you can avoid high latency times, because while one bank is delivering data, the memory controller can already send addresses for another bank.

Prefetch

The significantly lower speed of a DRAM compared to an SRAM is due to the structure and functionality of the DRAM. (Long word lines must be charged, a read cell can only output its charge slowly to the bit line, the read content must be evaluated and written back.) Although these times can generally be shortened using an internally modified structure, the storage density would decrease and so that the space requirement and thus the production price increase.

Instead, a trick is used to increase the external data transfer rate without having to increase the internal speed. In so-called prefetching , the data are read from several column addresses for each addressing and written to a parallel-serial converter ( shift register ). The data is output from this buffer with the higher (external) clock rate. This also explains the data bursts introduced with synchronous DRAMs and in particular their respective minimum burst length (it corresponds precisely to the length of the shift register used as a parallel-to-serial converter and thus the prefetch factor):

- SDR-SDRAM

- Prefetch = 1: 1 data bit per data pin is read out per read request.

- DDR SDRAM

- Prefetch = 2: 2 data bits per data pin are read out per read request and output in a data burst of length 2.

- DDR2 SDRAM

- Prefetch = 4: 4 data bits per data pin are read out per read request and output in a data burst of length 4.

- DDR3 and DDR4 SDRAM

- Prefetch = 8: 8 data bits per data pin are read out per read request and output in a data burst of length 8.

redundancy

As the storage density increases, the probability of defective storage cells increases. So-called redundant elements are provided in the chip design to increase the yield of functional DRAMs . These are additional row and column lines with corresponding memory cells. If defective memory cells are found during the test of the chips, the affected word or row line is deactivated. They are replaced by one (or more) word or row lines from the set of otherwise unused redundant elements (remapping).

The following procedures are used to permanently save this configuration change in the DRAM:

- With the help of a focused laser pulse, appropriately prepared contacts in the decoding circuits of the row or column address are vaporized ( laser fuse ).

- With the help of an electrical overvoltage pulse, electrical contacts are either opened ( e-fuse ) or closed (e.g. by destroying a thin insulating layer) ( anti e-fuse ).

In both cases, these permanent changes are used to program the address of the line to be replaced and the address of the redundant line to be used for it.

The number of redundant elements built into a DRAM design is approximately 1 percent.

The use of redundant elements to correct faulty memory cells must not be confused with active error correction based on parity bits or error-correcting codes (FEC). The error correction described here using redundant elements takes place once before the memory component is delivered to the customer. Subsequent errors (degradation of the component or transmission errors in the system) cannot be eliminated in this way.

See also: Memory module: ECC

Modules

Often entire memory modules are mistaken for the actual memory components . The difference is reflected in the size designation: DIMMs are measured in Mebi or Gibi byte (MiB or GiB), whereas the individual module chip on the DIMM is measured in Mebi or Gibi bit . Advances in manufacturing technology mean that manufacturers can accommodate more and more memory cells on the individual chips, so that 512 MiBit components are readily available. A memory module that complies with the standard is only created by interconnecting individual SDRAM chips.

history

| Year of introduction |

typ. burst rate (ns) |

DRAM type |

|---|---|---|

| 1970 | 00,60 … 300 | classic DRAM |

| 1987 | 00,40 … 50 | FPM-DRAM ( Fast Page Mode DRAM ) |

| 1995 | 00,20 … 30 | EDO-RAM ( Extended Data Output RAM ) |

| 1997 | 000,6… 15 | SDRAM ( Synchronous Dynamic RAM ) |

| 1999 | 00.83 … 1.88 | RDRAM ( Rambus Dynamic RAM ) |

| 2000 | 02.50… 5.00 | DDR-SDRAM (Double Data Rate SDRAM) |

| 2003 | 01.00 … 1.25 | GDDR2-SDRAM |

| 2004 | 00.94 … 2.50 | DDR2 SDRAM |

| 2004 | 00.38 … 0.71 | GDDR3-SDRAM |

| 2006 | 00.44 … 0.50 | GDDR4-SDRAM |

| 2007 | 00.47 … 1.25 | DDR3 SDRAM |

| 2008 | 00.12 … 0.27 | GDDR5-SDRAM |

| 2012 | 00.25 … 0.62 | DDR4 SDRAM |

| 2016 | 00.07 … 0.10 | GDDR5X-SDRAM |

| 2018 | 00.07 | GDDR6-SDRAM |

The first commercially available DRAM chip was the Type 1103 introduced by Intel in 1970 . It contained 1024 memory cells (1 KiBit ). The principle of the DRAM memory cell was developed in 1966 by Robert H. Dennard at the Thomas J. Watson Research Center of IBM .

Since then, the capacity of a DRAM chip has increased by a factor of 8 million and the access time has been reduced to a hundredth. Today (2014) DRAM ICs have capacities of up to 8 GiBit (single die) or 16 GiBit (twin die) and access times of 6 ns. The production of DRAM memory chips is one of the top-selling segments in the semiconductor industry. There is speculation with the products; there is a spot market .

In the beginning, DRAM memories were constructed from individual memory modules (chips) in DIL design. For 16 KiB of working memory (for example in the Atari 600XL or CBM 8032 ) 8 memory modules of type 4116 (16384 cells of 1 bit) or two modules of type 4416 (16384 cells of 4 bit) were required. For 64 KiB 8 blocks of type 4164 ( C64- I) or 2 blocks of type 41464 (C64-II) were needed.

IBM PCs were initially sold at 64 KiB as the minimum memory configuration. Nine building blocks of type 4164 were used here; the ninth block stores the parity bits .

Before the SIMMs came onto the market, there were, for example, motherboards for computers with Intel 80386 processors that could be equipped with 8 MiB of working memory made up of individual chips. For this, 72 individual chips of the type 411000 (1 MiBit) had to be pressed into the sockets. This was a lengthy and error-prone procedure. If the same board was to be equipped with only 4 MiB of RAM, with the considerably cheaper 41256 (256 KiB) chips being used instead of the 411000 type, 144 individual chips had to be inserted: 9 chips make 256 KiB, 16 such groups with 9 chips each resulted in 4 MiB. Larger chips were therefore soldered to form modules that required considerably less space.

application

random access memory

Normally the DRAM in the form of memory modules is used as the main memory of the processor . DRAMs are often classified according to the type of device interface . In the main applications, the interface types Fast Page Mode DRAM (FPM), Extended Data Output RAM (EDO), Synchronous DRAM (SDR), and Double Data Rate Synchronous DRAM (DDR) have developed in chronological order . The properties of these DRAM types are standardized by the JEDEC consortium . In addition, the Rambus DRAM interface exists parallel to SDR / DDR , which is mainly used for memory for servers .

Special applications

Special RAM is used as image and texture memory for graphics cards , for example GDDR3 (Graphics Double Data Rate SDRAM ).

The refreshing of the memory cells can be optimized by restricting them to a special area, so this can be set in the time of the line return in the case of an image memory, for example. It is also u. It can be tolerated if a single pixel temporarily shows the wrong color, so you don’t have to take the worst memory cell on the chip into account. Therefore — despite the same production technologies — significantly faster DRAMs can be produced.

Further types have been developed for special applications: Graphics DRAM (also Synchronous Graphics RAM, SGRAM) is optimized for use on graphics cards , for example, due to its higher data widths , but the basic functionality of a DDR DRAM, for example, is used. The forerunners of graphics RAM were video RAM (VRAM) — a Fast Page Mode RAM optimized for graphics applications with two ports instead of one — and then Window RAM (WRAM), which had EDO features and a dedicated display port .

DRAM types optimized for use in network components have been given the names Network-RAM , Fast-Cycle-RAM and Reduced Latency RAM by various manufacturers . In mobile applications, such as cell phones or PDAs , low energy consumption is important — for this purpose, mobile DRAMs are developed, in which the power consumption is reduced through special circuit technology and manufacturing technology. The pseudo-SRAM (also cellular RAM or 1T-SRAM = 1-transistor-SRAM from other manufacturers ) takes on a hybrid role : the memory itself is a DRAM that behaves like an SRAM to the outside world. This is achieved in that a logic circuit converts the SRAM-typical access mechanism to the DRAM control and the regular refreshing of the memory contents, which is fundamentally necessary for dynamic memories, is carried out by circuits contained in the module.

In the early days of the DRAMs, as these are often still in a ceramic — DIL — housing were built, there were craft solutions, using them as image sensors for DIY cameras. To do this, the metal cover on the ceramic housing was carefully removed, and the die was then directly underneath — without any potting compound. A lens was placed in front of it , which precisely reproduced the image on the die surface. If the chip was completely filled with 1 at the beginning of the exposure , i.e. all storage capacitors were charged, the charges were discharged at different speeds by incident light, depending on the intensity. After a certain (exposure) time, the cells were read out and the image was then interpreted in 1-bit resolution. For grayscale you had to take the same image several times with different exposure times. An additional complication resulted from the fact that the memory cells are not simply arranged according to their binary addresses in order to avoid crosstalk, but these address bits are deliberately “scrambled”. Therefore, after reading out, the image data first had to be brought into the correct arrangement with the inverse pattern. This is hardly possible with today’s chips, as they are usually embedded in plastic potting compound; in addition, digital cameras are now generally accessible and affordable.

Types

There are a variety of types of DRAM that have evolved over time:

- FPM RAM

- EDO RAM

- SDRAM

- DDR SDRAM

- RDRAM

A number of non-volatile RAM ( NVRAM ) technologies are currently under development, such as:

- FeRAM

- MRAM

- PCRAM

The storage capacity is specified in bits and bytes .

RAM used as main memory is often used in the form of memory modules :

- SIMM / PS / 2 SIMM

- DIMM / SO-DIMM

- MicroDIMM

The net total size of RAM modules used as main memory is practically always a power of 2.

literature

- Christof Windeck: Riegel-Reigen: Construction of current memory modules. In: c’t No. 7, 2006, p. 238 ( download of the journal article for a fee )

- Siemens AG (Ed.): Memory Components Data Book. Munich 1994.

- The DRAM story . In: SSCS IEEE SOLID-STATE CIRCUITS SOCIETY NEWS . tape 13 , no. 1 , 2008 ( complete edition as PDF [accessed August 1, 2009]).

Web links

German:

- Christian Hirsch: Compact working memory thanks to Z-RAM . In: heise online . August 15, 2007.

English:

-

Memory 1997 ( PDF , approx. 167 kB ) — Document from Integrated Circuit Engineering Corporation, ISBN 1-877750-59-X (166 kB)

- Section 7. DRAM Technology (PDF, approx. 770 kB) — Chapter 7 of «Memory 1997»

- The evolution of IBM CMOS DRAM Technology — IBM article , July 25, 1994

Individual evidence

- ↑ J. Alex Halderman, Seth D. Schoen, Nadia Heninger, William Clarkson, William Paul, Joseph A. Calandrino, Ariel J. Feldman, Jacob Appelbaum, Edward W. Felten: Lest We Remember: Cold Boot Attacks on Encryption Keys . In: Proc. 2008 USENIX Security Symposium. February 21, 2008, pp. 45-60.

In this article, we are going to learn How to Read File Line by Line in C language.We will read each line from the text file in each iteration.

C fscanf function

The fscanf function is available in the C library. This function is used to read formatted input from a stream. The syntax of fscanf function is:

int fscanf(FILE *stream, const char *format, …)

Parameters

- stream − This is the pointer to a FILE object that identifies the stream.

- format − This is the C string that contains one or more of the following items − Whitespace character, Non-whitespace character, and Format specifiers. A format specifier will be as [=%[*][width][modifiers]type=].

1. How to Read File Line by Line in C

Here we are making use of the fscanf function to read the text file.The first thing we are going to do is open the file in reading mode. So using fopen() function and “r” read mode we opened the file.The next step is to find the file stats like what is the size of the data this file contains. so we can allocate exact memory for the buffer that is going to hold the content of this file. We are using the stat() function to find the file size.

- Once we have the size and buffer allocated for this size, we start reading the file by using the fscanf() function.

- We keep reading the file line by line until we reach the end of the file. In fscanf function, we are passing n as the argument so we can read the text until we find a next line character.

- The code will look like this: “fscanf(in_file, “%[^n]”

C program to Read File Line by Line

To run this program, we need one text file with the name Readme.txt in the same folder where we have our code.The content of the file is:

Hello My name is John danny

#include <stdio.h>

#include <stdlib.h>

#include <sys/stat.h>

const char* filename = "Readme.txt";

int main(int argc, char *argv[])

{

FILE *in_file = fopen(filename, "r");

if (!in_file)

{

perror("fopen");

return 0;

}

struct stat sb;

if (stat(filename, &sb) == -1) {

perror("stat");

return 0;

}

char *textRead = malloc(sb.st_size);

int i = 1;

while (fscanf(in_file, "%[^n] ", textRead) != EOF)

{

printf("Line %d is %sn",i, textRead);

i++;

}

fclose(in_file);

return 0;

}

Output

Line 1 is Hello My name is Line 2 is John Line 3 is danny

Hi, I am new in VBScript. i used a VBScript for reading MSWord file word by word. here is the code of my Script.

Option Explicit Dim objWord Dim wordPath Dim currentDocument Dim numberOfWords Dim i Dim objDialog Set objDialog = CreateObject("UserAccounts.CommonDialog") objDialog.Filter = "VBScript Scripts|*.vbs|All Files|*.*" objDialog.FilterIndex = 1 objDialog.InitialDir = "C:" intResult = objDialog.ShowOpen If intResult = 0 Then Wscript.Quit Else Wscript.Echo objDialog.FileName End If wordPath = "C:Documents and SettingssapuserDesktopharry.doc" WScript.Echo "Extract Data from " & wordPath Set objWord = CreateObject("Word.Application") objWord.DisplayAlerts = 0 objWord.Documents.Open wordPath, false, true Set currentDocument = objWord.Documents(1) NumberOfWords = currentDocument.words.count WScript.Echo "There are " & NumberOfWords & " words " & vbCRLF For i = 1 to NumberOfWords WScript.Echo currentDocument.words(i) Next currentDocument.Close Set currentDocument = Nothing objWord.Quit Set objWord = Nothing

In this line we count the total number of words in my doc files

NumberOfWords = currentDocument.words.count

and this for loop display the contents of my doc file word by word

For i = 1 to NumberOfWords<br />

WScript.Echo currentDocument.words(i)<br />

Next<br />

But I want to read my doc file line by line. Is there any function which gets a line rather than a word?

Please suggest me a way to get a line by line display of my doc.

Thanks.

Updated 18-Oct-11 23:37pm

Try using Paragraphs

For Each p In currentDocument.Paragraphs WScript.Echo p.Range.Text Next p

This content, along with any associated source code and files, is licensed under The Code Project Open License (CPOL)

CodeProject,

20 Bay Street, 11th Floor Toronto, Ontario, Canada M5J 2N8

+1 (416) 849-8900

Magnetic-core memory was the predominant form of random-access computer memory for 20 years between about 1955 and 1975.

Such memory is often just called core memory, or, informally, core.

A 32 x 32 core memory plane storing 1024 bits (or 128 bytes) of data. The small black rings at the intersections of the grid wires, organised in four squares, are the ferrite cores.

Core memory uses toroids (rings) of a hard magnetic material (usually a semi-hard ferrite) as transformer cores, where each wire threaded through the core serves as a transformer winding. Two or more wires pass through each core. Magnetic hysteresis allows each of the cores to «remember», or store a state.

Each core stores one bit of information. A core can be magnetized in either the clockwise or counter-clockwise direction. The value of the bit stored in a core is zero or one according to the direction of that core’s magnetization. Electric current pulses in some of the wires through a core allow the direction of the magnetization in that core to be set in either direction, thus storing a one or a zero. Another wire through each core, the sense wire, is used to detect whether the core changed state.

The process of reading the core causes the core to be reset to a zero, thus erasing it. This is called destructive readout. When not being read or written, the cores maintain the last value they had, even if the power is turned off. Therefore, they are a type of non-volatile memory.

Using smaller cores and wires, the memory density of core slowly increased, and by the late 1960s a density of about 32 kilobits per cubic foot (about 0.9 kilobits per litre) was typical. However, reaching this density required extremely careful manufacture, which was almost always carried out by hand in spite of repeated major efforts to automate the process. The cost declined over this period from about $1 per bit to about 1 cent per bit. The introduction of the first semiconductor memory chips in the late 1960s, which initially created static random-access memory (SRAM), began to erode the market for core memory. The first successful dynamic random-access memory (DRAM), the Intel 1103, followed in 1970. Its availability in quantity at 1 cent per bit marked the beginning of the end for core memory.[1]

Improvements in semiconductor manufacturing led to rapid increases in storage capacity and decreases in price per kilobyte, while the costs and specs of core memory changed little. Core memory was driven from the market gradually between 1973 and 1978.

Depending on how it was wired, core memory could be exceptionally reliable. Read-only core rope memory, for example, was used on the mission-critical Apollo Guidance Computer essential to NASA’s successful Moon landings.

Although core memory is obsolete, computer memory is still sometimes called «core» even though it is made of semiconductors, particularly by people who had worked with machines having actual core memory. The files that result from saving the entire contents of memory to disk for inspection, which is nowadays commonly performed automatically when a major error occurs in a computer program, are still called «core dumps».

HistoryEdit

DevelopersEdit

The basic concept of using the square hysteresis loop of certain magnetic materials as a storage or switching device was known from the earliest days of computer development. Much of this knowledge had developed due to an understanding of transformers, which allowed amplification and switch-like performance when built using certain materials. The stable switching behavior was well known in the electrical engineering field, and its application in computer systems was immediate. For example, J. Presper Eckert and Jeffrey Chuan Chu had done some development work on the concept in 1945 at the Moore School during the ENIAC efforts.[2]

Robotics pioneer George Devol filed a patent[3] for the first static (non-moving) magnetic memory on 3 April 1946. Devol’s magnetic memory was further refined via 5 additional patents[4][5][6][7][8] and ultimately used in the first Industrial Robot. Frederick Viehe applied for various patents on the use of transformers for building digital logic circuits in place of relay logic beginning in 1947. A fully developed core system was patented in 1947, and later purchased by IBM in 1956.[9] This development was little-known, however, and the mainstream development of core is normally associated with three independent teams.

Substantial work in the field was carried out by the Shanghai-born American physicists An Wang and Way-Dong Woo, who created the pulse transfer controlling device in 1949.[10][11] The name referred to the way that the magnetic field of the cores could be used to control the switching of current; his patent focused on using cores to create delay-line or shift-register memory systems. Wang and Woo were working at Harvard University’s Computation Laboratory at the time, and the university was not interested in promoting inventions created in their labs. Wang was able to patent the system on his own.

The MIT Project Whirlwind computer required a fast memory system for real-time aircraft tracking. At first, an array of Williams tubes—a storage system based on cathode ray tubes—was used, but proved temperamental and unreliable. Several researchers in the late 1940s conceived the idea of using magnetic cores for computer memory, but MIT computer engineer Jay Forrester received the principal patent for his invention of the coincident-current core memory that enabled the 3D storage of information.[12][13] William Papian of Project Whirlwind cited one of these efforts, Harvard’s «Static Magnetic Delay Line», in an internal memo. The first core memory of 32 × 32 × 16 bits was installed on Whirlwind in the summer of 1953. Papian stated: «Magnetic-Core Storage has two big advantages: (1) greater reliability with a consequent reduction in maintenance time devoted to storage; (2) shorter access time (core access time is 9 microseconds: tube access time is approximately 25 microseconds) thus increasing the speed of computer operation.»[14]

In April 2011, Forrester recalled, «the Wang use of cores did not have any influence on my development of random-access memory. The Wang memory was expensive and complicated. As I recall, which may not be entirely correct, it used two cores per binary bit and was essentially a delay line that moved a bit forward. To the extent that I may have focused on it, the approach was not suitable for our purposes.» He describes the invention and associated events, in 1975.[15] Forrester has since observed, «It took us about seven years to convince the industry that random-access magnetic-core memory was the solution to a missing link in computer technology. Then we spent the following seven years in the patent courts convincing them that they had not all thought of it first.»[16]

A third developer involved in the early development of core was Jan A. Rajchman at RCA. A prolific inventor, Rajchman designed a unique core system using ferrite bands wrapped around thin metal tubes,[17] building his first examples using a converted aspirin press in 1949.[9] Rajchman later developed versions of the Williams tube and led development of the Selectron.[18]

Two key inventions led to the development of magnetic core memory in 1951. The first, An Wang’s, was the write-after-read cycle, which solved the problem of how to use a storage medium in which the act of reading erased the data read, enabling the construction of a serial, one-dimensional shift register (of 50 bits), using two cores to store a bit. A Wang core shift register is in the Revolution exhibit at the Computer History Museum. The second, Forrester’s, was the coincident-current system, which enabled a small number of wires to control a large number of cores enabling 3D memory arrays of several million bits. The first use of core was in the Whirlwind computer, and Project Whirlwind’s «most famous contribution was the random-access, magnetic core storage feature.»[19] Commercialization followed quickly. Magnetic core was used in peripherals of the ENIAC in 1953,[20] the IBM 702[21] delivered in July 1955, and later in the 702 itself. The IBM 704 (1954) and the Ferranti Mercury (1957) used magnetic-core memory.

It was during the early 1950s that Seeburg Corporation developed one of the first commercial applications of coincident-current core memory storage in the «Tormat» memory of its new range of jukeboxes, starting with the V200 developed in 1953 and released in 1955.[22] Numerous uses in computing, telephony and industrial process control followed.

Patent disputesEdit

Wang’s patent was not granted until 1955, and by that time magnetic-core memory was already in use. This started a long series of lawsuits, which eventually ended when IBM bought the patent outright from Wang for US$500,000.[23] Wang used the funds to greatly expand Wang Laboratories, which he had co-founded with Dr. Ge-Yao Chu, a schoolmate from China.

MIT wanted to charge IBM $0.02 per bit royalty on core memory. In 1964, after years of legal wrangling, IBM paid MIT $13 million for rights to Forrester’s patent—the largest patent settlement to that date.[24][25]

Production economicsEdit

In 1953, tested but not-yet-strung cores cost US$0.33 each. As manufacturing volume increased, by 1970 IBM was producing 20 billion cores per year, and the price per core fell to US$0.0003. Core sizes shrank over the same period from around 0.1 inches (2.5 mm) diameter in the 1950s to 0.013 inches (0.33 mm) in 1966.[26] The power required to flip the magnetization of one core is proportional to the volume, so this represents a drop in power consumption by a factor of 125.

The cost of complete core memory systems was dominated by the cost of stringing the wires through the cores. Forrester’s coincident-current system required one of the wires to be run at 45 degrees to the cores, which proved difficult to wire by machine, so that core arrays had to be assembled under microscopes by workers with fine motor control.

In 1956, a group at IBM filed for a patent on a machine to automatically thread the first few wires through each core. This machine held the full plane of cores in a «nest» and then pushed an array of hollow needles through the cores to guide the wires.[27] Use of this machine reduced the time taken to thread the straight X and Y select lines from 25 hours to 12 minutes on a 128 by 128 core array.[28]

Smaller cores made the use of hollow needles impractical, but there were numerous advances in semi-automatic core threading. Support nests with guide channels were developed. Cores were permanently bonded to a backing sheet «patch» that supported them during manufacture and later use. Threading needles were butt welded to the wires, so the needle and wire diameters were the same, and efforts were made to entirely eliminate the use of needles.[29][30]

The most important change, from the point of view of automation, was the combination of the sense and inhibit wires, eliminating the need for a circuitous diagonal sense wire. With small changes in layout, this also allowed much tighter packing of the cores in each patch.[31][32]

By the early 1960s, the cost of core fell to the point that it became nearly universal as main memory, replacing both inexpensive low-performance drum memory and costly high-performance systems using vacuum tubes, and later discrete transistors as memory. The cost of core memory declined sharply over the lifetime of the technology: costs began at roughly US$1.00 per bit and dropped to roughly US$0.01 per bit. Core was replaced with integrated semiconductor RAM chips in the 1970s.

An example of the scale, economics, and technology of core memory in the 1960s was the 256K 36-bit word (1.2 MiB[33]) core memory unit installed on the PDP-6 at the MIT Artificial Intelligence Laboratory by 1967.[34] This was considered «unimaginably huge» at the time, and nicknamed the «Moby Memory».[35] It cost $380,000 ($0.04/bit) and was 69 inches wide, 50 inches tall, and 25 inches deep with its supporting circuitry (189 kilobits/cubic foot = 6.7 kilobits/litre). Its cycle time was 2.75 μs.[36][37][38]

DescriptionEdit

Diagram of a 4×4 plane of magnetic core memory in an X/Y line coincident-current setup. X and Y are drive lines, S is sense, Z is inhibit. Arrows indicate the direction of current for writing.

Close-up of a core plane. The distance between the rings is roughly 1 mm (0.04 in). The green horizontal wires are X; the Y wires are dull brown and vertical, toward the back. The sense wires are diagonal, colored orange, and the inhibit wires are vertical twisted pairs.

The term «core» comes from conventional transformers whose windings surround a magnetic core. In core memory, the wires pass once through any given core—they are single-turn devices. The properties of materials used for memory cores are dramatically different from those used in power transformers. The magnetic material for a core memory requires a high degree of magnetic remanence, the ability to stay highly magnetized, and a low coercivity so that less energy is required to change the magnetization direction. The core can take two states, encoding one bit. The core memory contents are retained even when the memory system is powered down (non-volatile memory). However, when the core is read, it is reset to a «zero» value. Circuits in the computer memory system then restore the information in an immediate re-write cycle.

How core memory worksEdit

One of three inter-connected modules that make up an Omnibus-based (PDP 8/e/f/m) PDP-8 core memory plane.

One of three inter-connected modules that make up an Omnibus-based PDP-8 core memory plane. This is the middle of the three and contains the array of actual ferrite cores.

One of three inter-connected modules that make up an Omnibus-based PDP-8 core memory plane.

The most common form of core memory, X/Y line coincident-current, used for the main memory of a computer, consists of a large number of small toroidal ferrimagnetic ceramic ferrites (cores) held together in a grid structure (organized as a «stack» of layers called planes), with wires woven through the holes in the cores’ centers. In early systems there were four wires: X, Y, Sense, and Inhibit, but later cores combined the latter two wires into one Sense/Inhibit line.[31] Each toroid stored one bit (0 or 1). One bit in each plane could be accessed in one cycle, so each machine word in an array of words was spread over a «stack» of planes. Each plane would manipulate one bit of a word in parallel, allowing the full word to be read or written in one cycle.

Core relies on the «square loop» properties of the ferrite material used to make the toroids. An electric current in a wire that passes through a core creates a magnetic field. Only a magnetic field greater than a certain intensity («select») can cause the core to change its magnetic polarity. To select a memory location, one of the X and one of the Y lines are driven with half the current («half-select») required to cause this change. Only the combined magnetic field generated where the X and Y lines cross (a logical AND function) is sufficient to change the state; other cores will see only half the needed field («half-selected»), or none at all. By driving the current through the wires in a particular direction, the resulting induced field forces the selected core’s magnetic flux to circulate in one direction or the other (clockwise or counterclockwise). One direction is a stored 1, while the other is a stored 0.

The toroidal shape of a core is preferred since the magnetic path is closed, there are no magnetic poles and thus very little external flux. This allows the cores to be packed closely together without allowing their magnetic fields to interact. The alternating 45-degree positioning used in early core arrays was necessitated by the diagonal sense wires. With the elimination of these diagonal wires, tighter packing was possible.[32]

Reading and writingEdit

Diagram of the hysteresis curve for a magnetic memory core during a read operation. Sense line current pulse is high («1») or low («0») depending on original magnetization state of the core.

To read a bit of core memory, the circuitry tries to flip the bit to the polarity assigned to the 0 state, by driving the selected X and Y lines that intersect at that core.

- If the bit was already 0, the physical state of the core is unaffected.

- If the bit was previously 1, then the core changes magnetic polarity. This change, after a delay, induces a voltage pulse into the Sense line.

The detection of such a pulse means that the bit had most recently contained a 1. Absence of the pulse means that the bit had contained a 0. The delay in sensing the voltage pulse is called the access time of the core memory.

Following any such read, the bit contains a 0. This illustrates why a core memory access is called a destructive read: Any operation that reads the contents of a core erases those contents, and they must immediately be recreated.

To write a bit of core memory, the circuitry assumes there has been a read operation and the bit is in the 0 state.

- To write a 1 bit, the selected X and Y lines are driven, with current in the opposite direction as for the read operation. As with the read, the core at the intersection of the X and Y lines changes magnetic polarity.

- To write a 0 bit, two methods can be applied. The first one is the same as reading process with current in the original direction. The second has reversed logic. Write 0 bit, in other words, is to inhibit the writing of a 1 bit. The same amount of current is also sent through the Inhibit line. This reduces the net current flowing through the respective core to half the select current, inhibiting change of polarity.

The access time plus the time to rewrite is the memory cycle time.

The Sense wire is used only during the read, and the Inhibit wire is used only during the write. For this reason, later core systems combined the two into a single wire, and used circuitry in the memory controller to switch the function of the wire. However, when Sense wire crosses too many cores, the half select current can also induce a considerable voltage across the whole line due to the superposition of the voltage at each single core. This potential risk of «misread» limits the minimum number of the Sense wire. Increasing Sense wires requires more decode circuits.

Core memory controllers were designed so that every read was followed immediately by a write (because the read forced all bits to 0, and because the write assumed this had happened). Computers began to take advantage of this fact. For example, a value in memory could be read and incremented (as for example by the AOS instruction on the PDP-6) almost as quickly as it could be read; the hardware simply incremented the value between the read phase and the write phase of a single memory cycle (perhaps signalling the memory controller to pause briefly in the middle of the cycle). This might be twice as fast as the process of obtaining the value with a read-write cycle, incrementing the value in some processor register, and then writing the new value with another read-write cycle.

Other forms of core memoryEdit

A 10.8×10.8 cm plane of magnetic core memory with 64 x 64 bits (4 Kb), as used in a CDC 6600. Inset shows word line architecture with two wires per bit

Word line core memory was often used to provide register memory. Other names for this type are linear select and 2-D. This form of core memory typically wove three wires through each core on the plane, word read, word write, and bit sense/write. To read or clear words, the full current is applied to one or more word read lines; this clears the selected cores and any that flip induce voltage pulses in their bit sense/write lines. For read, normally only one word read line would be selected; but for clear, multiple word read lines could be selected while the bit sense/write lines ignored. To write words, the half current is applied to one or more word write lines, and half current is applied to each bit sense/write line for a bit to be set. In some designs, the word read and word write lines were combined into a single wire, resulting in a memory array with just two wires per bit. For write, multiple word write lines could be selected. This offered a performance advantage over X/Y line coincident-current in that multiple words could be cleared or written with the same value in a single cycle. A typical machine’s register set usually used only one small plane of this form of core memory. Some very large memories were built with this technology, for example the Extended Core Storage (ECS) auxiliary memory in the CDC 6600, which was up to 2 million 60-bit words.

Another form of core memory called core rope memory provided read-only storage. In this case, the cores, which had more linear magnetic materials, were simply used as transformers; no information was actually stored magnetically within the individual cores. Each bit of the word had one core. Reading the contents of a given memory address generated a pulse of current in a wire corresponding to that address. Each address wire was threaded either through a core to signify a binary [1], or around the outside of that core, to signify a binary [0]. As expected, the cores were much larger physically than those of read-write core memory. This type of memory was exceptionally reliable. An example was the Apollo Guidance Computer used for the NASA Moon landings.

Physical characteristicsEdit

The performance of early core memories can be characterized in today’s terms as being very roughly comparable to a clock rate of 1 MHz (equivalent to early 1980s home computers, like the Apple II and Commodore 64). Early core memory systems had cycle times of about 6 µs, which had fallen to 1.2 µs by the early 1970s, and by the mid-70s it was down to 600 ns (0.6 µs). Some designs had substantially higher performance: the CDC 6600 had a memory cycle time of 1.0 µs in 1964, using cores that required a half-select current of 200 mA.[39] Everything possible was done in order to decrease access times and increase data rates (bandwidth), including the simultaneous use of multiple grids of core, each storing one bit of a data word. For instance, a machine might use 32 grids of core with a single bit of the 32-bit word in each one, and the controller could access the entire 32-bit word in a single read/write cycle.

Core memory is non-volatile storage—it can retain its contents indefinitely without power. It is also relatively unaffected by EMP and radiation. These were important advantages for some applications like first-generation industrial programmable controllers, military installations and vehicles like fighter aircraft, as well as spacecraft, and led to core being used for a number of years after availability of semiconductor MOS memory (see also MOSFET). For example, the Space Shuttle IBM AP-101B flight computers used core memory, which preserved the contents of memory even through the Challenger‘s disintegration and subsequent plunge into the sea in 1986.[40] Another characteristic of early core was that the coercive force was very temperature-sensitive; the proper half-select current at one temperature is not the proper half-select current at another temperature. So a memory controller would include a temperature sensor (typically a thermistor) to adjust the current levels correctly for temperature changes. An example of this is the core memory used by Digital Equipment Corporation for their PDP-1 computer; this strategy continued through all of the follow-on core memory systems built by DEC for their PDP line of air-cooled computers. Another method of handling the temperature sensitivity was to enclose the magnetic core «stack» in a temperature controlled oven. Examples of this are the heated-air core memory of the IBM 1620 (which could take up to 30 minutes to reach operating temperature, about 106 °F (41 °C) and the heated-oil-bath core memory of the IBM 7090, early IBM 7094s, and IBM 7030.

Core was heated instead of cooled because the primary requirement was a consistent temperature, and it was easier (and cheaper) to maintain a constant temperature well above room temperature than one at or below it.

In 1980, the price of a 16 kW (kiloword, equivalent to 32 kB) core memory board that fitted into a DEC Q-bus computer was around US$3,000. At that time, core array and supporting electronics fit on a single printed circuit board about 25 × 20 cm in size, the core array was mounted a few mm above the PCB and was protected with a metal or plastic plate.

Diagnosing hardware problems in core memory required time-consuming diagnostic programs to be run. While a quick test checked if every bit could contain a one and a zero, these diagnostics tested the core memory with worst-case patterns and had to run for several hours. As most computers had just a single core memory board, these diagnostics also moved themselves around in memory, making it possible to test every bit. An advanced test was called a «Shmoo test» in which the half-select currents were modified along with the time at which the sense line was tested («strobed»). The data plot of this test seemed to resemble a cartoon character called «Shmoo,» and the name stuck. In many occasions, errors could be resolved by gently tapping the printed circuit board with the core array on a table. This slightly changed the positions of the cores along the wires running through them, and could fix the problem. The procedure was seldom needed, as core memory proved to be very reliable compared to other computer components of the day.

-

This microSDHC card holds 8 billion bytes (8 GB). It rests on a section of magnetic-core memory that uses 64 cores to hold eight bytes. The microSDHC card holds over one billion times more bytes in much less physical space.

-

Magnetic-core memory, 18×24 bits, with a US quarter for scale

-

Magnetic-core memory close-up

See alsoEdit

- Bubble memory

- Core dump

- Core rope memory

- Delay-line memory

- Electronic calculators

- Ferroelectric RAM

- Magnetoresistive random-access memory

- Read-mostly memory (RMM)

- Thin-film memory

- Twistor memory

ReferencesEdit

- ^ Bellis, Mary (23 February 2018). «Who Invented the Intel 1103 DRAM Chip?». Thought Co. US.

- ^ Eckert, J. Presper (October 1953). «A Survey of Digital Computer Memory Systems». Proceedings of the IRE. US: IEEE. 41 (10): 1393–1406. doi:10.1109/JRPROC.1953.274316. ISSN 0096-8390. S2CID 8564797.

- ^ «Magnetic Process Control No. 2590091» (PDF). Georgedevol.com. 25 March 1952. Retrieved 15 November 2021.

- ^ «Magnetic Storage ands Sensing Device No. 2741757» (PDF). Georgedevol.com. 25 March 1952. Retrieved 15 November 2021.

- ^ «Sensing Device for Magnetic Record No. 2926844» (PDF). Georgedevol.com. 25 March 1952. Retrieved 15 November 2021.

- ^ «Magnetic Storage Devices No. 3035253» (PDF). Georgedevol.com. 25 March 1952. Retrieved 15 November 2021.

- ^ «Coincidence Detectors No. 3016465» (PDF). Georgedevol.com. 25 March 1952. Retrieved 15 November 2021.

- ^ «Ferroresonant Devices No. 3246219» (PDF). Georgedevol.com. 25 March 1952. Retrieved 15 November 2021.

- ^ a b Reilly, Edwin D. (2003). Milestones in computer science and information technology. Westport, CT: Greenwood Press. p. 164. ISBN 1-57356-521-0.

- ^ «Wang Interview, An Wang’s Early Work in Core Memories». Datamation. US: Technical Publishing Company: 161–163. March 1976.

- ^ US 2708722, Wang, An, «Pulse Transfer Controlling Device», issued 17 May 2020.

- ^ Forrester, Jay W. (1951). «Digital Information In Three Dimensions Using Magnetic Cores». Journal of Applied Physics. 22 (22). doi:10.1063/1.1699817.

- ^ US 2736880, Forrester, Jay W., «Multicoordinate digital information storage device», issued 28 February 1956

- ^ «Whirlwind» (PDF). The Computer Museum Report. Massachusetts: The Computer Museum: 13. Winter 1983 – via Microsoft.

- ^ Evans, Christopher (July 1983). «Jay W. Forrester Interview». Annals of the History of Computing. 5 (3): 297–301. doi:10.1109/mahc.1983.10081. S2CID 25146240.

- ^ Kleiner, Art (4 February 2009). «Jay Forrester’s Shock to the System». The MIT Sloan Review. US. Retrieved 1 April 2018.

- ^ Jan A. Rajchman, Magnetic System, U.S. Patent 2,792,563, granted 14 May 1957.

- ^ Hittinger, William (1992). «Jan A. Rajchman». Memorial Tributes. US: National Academy of Engineering. 5: 229.

- ^ Redmond, Kent C.; Smith, Thomas M. (1980). Project Whirlwind — The History of a Pioneer Computer. Bedford, Mass.: Digital Press. p. 215. ISBN 0932376096.

- ^ Auerbach, Isaac L. (2 May 1952). «A static magnetic memory system for the ENIAC». Proceedings of the 1952 ACM national meeting (Pittsburgh) on — ACM ’52. pp. 213–222. doi:10.1145/609784.609813. ISBN 9781450373623. S2CID 17518946.

- ^ Pugh, Emerson W.; Johnson, Lyle R.; Palmer, John H. (1991). IBM’s 360 and Early 370 Systems. MIT Press. p. 32. ISBN 978-0-262-51720-1.

- ^ Clarence Schultz and George Boesen, Selectors for Automatic Phonographs, U.S. Patent 2,792,563, granted Feb. 2, 1960.

- ^ «An Wang Sells Core Memory Patent to IBM». US: Computer History Museum. Retrieved 12 April 2010.

- ^ «Magnetic Core Memory». CHM Revolution. Computer History Museum. Retrieved 1 April 2018.

- ^ Pugh, Johnson & Palmer 1991, p. 182

- ^ Pugh, Johnson & Palmer 1991, pp. 204–6

- ^ Walter P. Shaw and Roderick W. Link, Method and Apparatus for Threading Perforated Articles, U.S. Patent 2,958,126, granted Nov. 1, 1960.

- ^ Bashe, Charles J.; Johnson, Lyle R.; Palmer, John H. (1986). IBM’s Early Computers. Cambridge, MA: MIT Press. p. 268. ISBN 0-262-52393-0.

- ^ Robert L. Judge, Wire Threading Method and Apparatus, U.S. Patent 3,314,131, granted Apr. 18, 1967.

- ^ Ronald A. Beck and Dennis L. Breu, Core Patch Stringing Method, U.S. Patent 3,872,581, granted Mar. 25, 1975.

- ^ a b Creighton D. Barnes, et al., Magnetic core storage device having a single winding for both the sensing and inhibit function, U.S. Patent 3,329,940, granted 4 July 1967.

- ^ a b Victor L. Sell and Syed Alvi, High Density Core Memory Matrix, U.S. Patent 3,711,839, granted Jan. 16, 1973.

- ^ Internally, the Moby Memory had 40 bits per word, but they were not exposed to the PDP-10 processor.

- ^ Project MAC. Progress Report IV. July 1966-July 1967 (PDF) (Report). Massachusetts Institute of Technology. p. 18. 681342. Archived from the original (PDF) on 8 May 2021. Retrieved 7 December 2020.

- ^ Eric S. Raymond, Guy L. Steele, The New Hacker’s Dictionary, 3rd edition, 1996, ISBN 0262680920, based on the Jargon File, s.v. ‘moby’, p. 307

- ^ «FABRI-TEK Mass Core ‘Moby’ Memory». Computer History Museum. US. 102731715. Retrieved 7 December 2020.

- ^ Krakauer, Lawrence J. «Moby Memory». Retrieved 7 December 2020.

- ^ Steven Levy, Hackers: Heroes of the Computer Revolution, 2010 (25th anniversary edition), ISBN 1449393748, p. 98

- ^ «Section 4». Control Data 6600 Training Manual. Control Data Corporation. June 1965. Document number 60147400.

- ^ «Magnetic Core Memory». US: National High Magnetic Field Laboratory: Museum of Electricity and Magnetism. Archived from the original on 10 June 2010.

External linksEdit

Look up core memory in Wiktionary, the free dictionary.

- Interactive Java Tutorial — Magnetic Core Memory National High Magnetic Field Laboratory

- Core Memory at Columbia University

- «Magnetic Cores». Digital Computer Basics (Rate Training Manual). Naval Education and Training Command. 1978. pp. 95–. NAVEDTRA 10088-B.

- Core Memory on the PDP-11

- Core memory and other early memory types accessed 15 April 2006

- Coincident Current Ferrite Core Memories Byte magazine, July 1976

- Casio AL-1000 calculator – Shows close-ups of the magnetic core memory in this desktop electronic calculator from the mid-1960s.

- Still used core memory in multiple devices in a German computer museum

- Werner, G.E.; Whalen, R.M.; Lockhart, N.F.; Flaker, R.C. (March 1967). «A 110-Nanosecond Ferrite Core Memory» (PDF). IBM Journal of Research and Development. 11 (2): 153–161. doi:10.1147/rd.112.0153. Archived from the original (PDF) on 26 February 2009.

- Background on core memory for computers

13 May 2017

It’s easy to eat a lot of memory when parsing text in Node, especially when

reading from a stream.

Suppose you’re reading data from the DARPA Intrusion Detection Data

Sets, and you want to compute the mean time of an attack. Assume you’ve

already processed the data so it’s just a list of timestamps as hours, minutes,

and seconds.

10:09:57

02:13:20

00:03:36

10:21:33

19:37:32

Here’s JavaScript that parses each timestamp to get the total number of seconds

and a count of the number of timestamps.

let total = 0;

let count = 0;

const parse = (timestamp) => {

const [h, m, s] = timestamp.split(':');

total += (Number(h) || 0) * 60 * 60;

total += (Number(m) || 0) * 60;

total += (Number(s) || 0);

count += 1;

};

With that, you can compute the mean as Math.ceil(total / count). If you’re

reading timestamps from process.stdin in Node, you can store them in

a string and compute the mean once you’ve seen them all.

let text = '';

process.stdin.setEncoding('utf-8');

process.stdin.on('data', (data) => {

if (data) {

text += data;

}

});

process.stdin.on('end', () => {

const timestamps = text.split("n");

timestamps.forEach(parse);

const mean = Math.ceil(total / count);

console.log(`${mean} seconds`);

});

The gotcha is that all that text is kept in memory. Node has a maximum String

size, and it’ll throw exceptions if you try and read too much data. Running on

an old iMac, I can read about 512 MB before Node crashes.

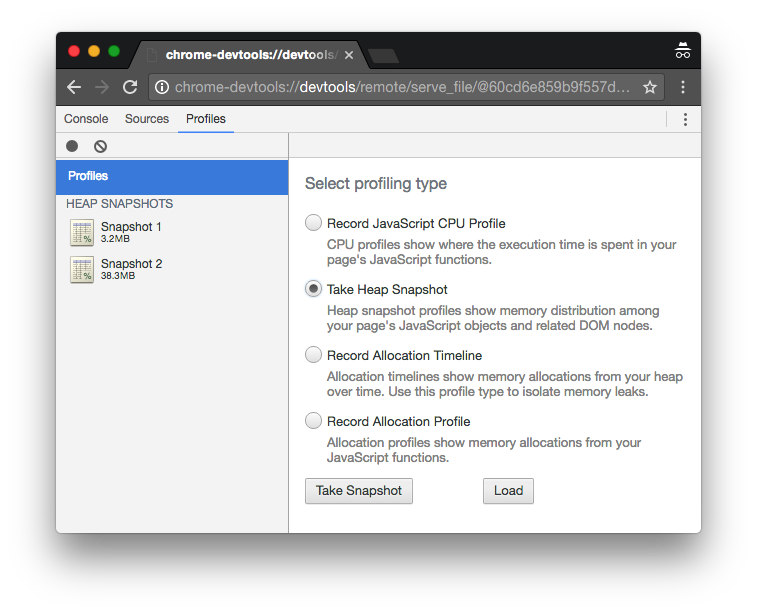

To figure out how much memory this used, I ran the code above through Chrome

DevTools on a 34 MB input file and captured two heap snapshots.

$ du -h data.txt

34M data.txt

$ node --inspect --debug-brk mean-time.js < data.txt

To start debugging, open the following URL in Chrome:

chrome-devtools://devtools/remote/serve_file/...

Debugger attached.

Waiting for the debugger to disconnect...

The first snapshot is the amount of memory used on startup, before any data has

been processed. It’s 3.2 MB. The second snapshot is the amount of memory used

after all the data has been processed. It’s 38.3 MB.

Which means most of the memory is being used to store all that text.

Fortunately, there’s an easy workaround. Check for complete timestamps as each

new chunk of data comes in and parse each one on the fly.

let text = '';

process.stdin.setEncoding('utf-8');

process.stdin.on('data', (data) => {

if (data) {

text += data;

const timestamps = text.split("n");

if (timestamps.length > 1) {

text = timestamps.splice(-1, 1)[0];

timestamps.forEach(parse);

}

}

});

process.stdin.on('end', () => {

parse(text);

const mean = Math.ceil(total / count);

console.log(`${mean} seconds`);

});

This code splits the buffered text on newlines as it arrives. It parses

every timestamp but the last, which is used to start the next buffer. At the

end, it parses anything remaining. Saving that the last timestamp until the end

means that if we get a partial timestamp, like 02:13:, we won’t try to parse

it until we see the whole thing.

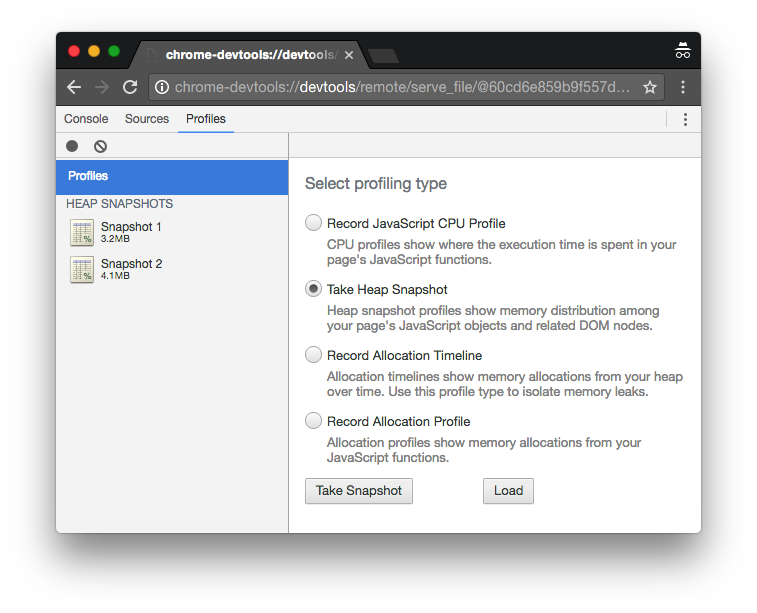

I ran the same experiment to see if memory use improved.

$ node --inspect --debug-brk mean-time.js < data.txt

To start debugging, open the following URL in Chrome:

chrome-devtools://devtools/remote/serve_file/...

Debugger attached.

Waiting for the debugger to disconnect...

As before, the first snapshot is the amount of memory used on startup, before

any data has been processed. It’s still 3.2 MB. The second snapshot is the

amount of memory used after all the data has been processed. This time it’s only

4.1 MB. That’s 34.2 MB of memory saved!

By processing data as it becomes available, you can read data line-by-line and

keep memory use low.

PRIORITY CLAIM

This application claims priority from European patent application No. 02425084.7, filed Feb. 20, 2002, which is incorporated herein by reference.

TECHNICAL FIELD

The present invention relates generally to the field of semiconductor memories, particularly non-volatile memories. More particularly, the invention relates to electrically erasable and programmable non-volatile memories, such as flash memories.

BACKGROUND OF THE INVENTION