From Wikipedia, the free encyclopedia

In computing, a word is the natural unit of data used by a particular processor design. A word is a fixed-sized datum handled as a unit by the instruction set or the hardware of the processor. The number of bits or digits[a] in a word (the word size, word width, or word length) is an important characteristic of any specific processor design or computer architecture.

The size of a word is reflected in many aspects of a computer’s structure and operation; the majority of the registers in a processor are usually word-sized and the largest datum that can be transferred to and from the working memory in a single operation is a word in many (not all) architectures. The largest possible address size, used to designate a location in memory, is typically a hardware word (here, «hardware word» means the full-sized natural word of the processor, as opposed to any other definition used).

Documentation for older computers with fixed word size commonly states memory sizes in words rather than bytes or characters. The documentation sometimes uses metric prefixes correctly, sometimes with rounding, e.g., 65 kilowords (KW) meaning for 65536 words, and sometimes uses them incorrectly, with kilowords (KW) meaning 1024 words (210) and megawords (MW) meaning 1,048,576 words (220). With standardization on 8-bit bytes and byte addressability, stating memory sizes in bytes, kilobytes, and megabytes with powers of 1024 rather than 1000 has become the norm, although there is some use of the IEC binary prefixes.

Several of the earliest computers (and a few modern as well) use binary-coded decimal rather than plain binary, typically having a word size of 10 or 12 decimal digits, and some early decimal computers have no fixed word length at all. Early binary systems tended to use word lengths that were some multiple of 6-bits, with the 36-bit word being especially common on mainframe computers. The introduction of ASCII led to the move to systems with word lengths that were a multiple of 8-bits, with 16-bit machines being popular in the 1970s before the move to modern processors with 32 or 64 bits.[1] Special-purpose designs like digital signal processors, may have any word length from 4 to 80 bits.[1]

The size of a word can sometimes differ from the expected due to backward compatibility with earlier computers. If multiple compatible variations or a family of processors share a common architecture and instruction set but differ in their word sizes, their documentation and software may become notationally complex to accommodate the difference (see Size families below).

Uses of words[edit]

Depending on how a computer is organized, word-size units may be used for:

- Fixed-point numbers

- Holders for fixed point, usually integer, numerical values may be available in one or in several different sizes, but one of the sizes available will almost always be the word. The other sizes, if any, are likely to be multiples or fractions of the word size. The smaller sizes are normally used only for efficient use of memory; when loaded into the processor, their values usually go into a larger, word sized holder.

- Floating-point numbers

- Holders for floating-point numerical values are typically either a word or a multiple of a word.

- Addresses

- Holders for memory addresses must be of a size capable of expressing the needed range of values but not be excessively large, so often the size used is the word though it can also be a multiple or fraction of the word size.

- Registers

- Processor registers are designed with a size appropriate for the type of data they hold, e.g. integers, floating-point numbers, or addresses. Many computer architectures use general-purpose registers that are capable of storing data in multiple representations.

- Memory–processor transfer

- When the processor reads from the memory subsystem into a register or writes a register’s value to memory, the amount of data transferred is often a word. Historically, this amount of bits which could be transferred in one cycle was also called a catena in some environments (such as the Bull GAMMA 60 [fr]).[2][3] In simple memory subsystems, the word is transferred over the memory data bus, which typically has a width of a word or half-word. In memory subsystems that use caches, the word-sized transfer is the one between the processor and the first level of cache; at lower levels of the memory hierarchy larger transfers (which are a multiple of the word size) are normally used.

- Unit of address resolution

- In a given architecture, successive address values designate successive units of memory; this unit is the unit of address resolution. In most computers, the unit is either a character (e.g. a byte) or a word. (A few computers have used bit resolution.) If the unit is a word, then a larger amount of memory can be accessed using an address of a given size at the cost of added complexity to access individual characters. On the other hand, if the unit is a byte, then individual characters can be addressed (i.e. selected during the memory operation).

- Instructions

- Machine instructions are normally the size of the architecture’s word, such as in RISC architectures, or a multiple of the «char» size that is a fraction of it. This is a natural choice since instructions and data usually share the same memory subsystem. In Harvard architectures the word sizes of instructions and data need not be related, as instructions and data are stored in different memories; for example, the processor in the 1ESS electronic telephone switch has 37-bit instructions and 23-bit data words.

Word size choice[edit]

When a computer architecture is designed, the choice of a word size is of substantial importance. There are design considerations which encourage particular bit-group sizes for particular uses (e.g. for addresses), and these considerations point to different sizes for different uses. However, considerations of economy in design strongly push for one size, or a very few sizes related by multiples or fractions (submultiples) to a primary size. That preferred size becomes the word size of the architecture.

Character size was in the past (pre-variable-sized character encoding) one of the influences on unit of address resolution and the choice of word size. Before the mid-1960s, characters were most often stored in six bits; this allowed no more than 64 characters, so the alphabet was limited to upper case. Since it is efficient in time and space to have the word size be a multiple of the character size, word sizes in this period were usually multiples of 6 bits (in binary machines). A common choice then was the 36-bit word, which is also a good size for the numeric properties of a floating point format.

After the introduction of the IBM System/360 design, which uses eight-bit characters and supports lower-case letters, the standard size of a character (or more accurately, a byte) becomes eight bits. Word sizes thereafter are naturally multiples of eight bits, with 16, 32, and 64 bits being commonly used.

Variable-word architectures[edit]

Early machine designs included some that used what is often termed a variable word length. In this type of organization, an operand has no fixed length. Depending on the machine and the instruction, the length might be denoted by a count field, by a delimiting character, or by an additional bit called, e.g., flag, or word mark. Such machines often use binary-coded decimal in 4-bit digits, or in 6-bit characters, for numbers. This class of machines includes the IBM 702, IBM 705, IBM 7080, IBM 7010, UNIVAC 1050, IBM 1401, IBM 1620, and RCA 301.

Most of these machines work on one unit of memory at a time and since each instruction or datum is several units long, each instruction takes several cycles just to access memory. These machines are often quite slow because of this. For example, instruction fetches on an IBM 1620 Model I take 8 cycles (160 μs) just to read the 12 digits of the instruction (the Model II reduced this to 6 cycles, or 4 cycles if the instruction did not need both address fields). Instruction execution takes a variable number of cycles, depending on the size of the operands.

Word, bit and byte addressing[edit]

The memory model of an architecture is strongly influenced by the word size. In particular, the resolution of a memory address, that is, the smallest unit that can be designated by an address, has often been chosen to be the word. In this approach, the word-addressable machine approach, address values which differ by one designate adjacent memory words. This is natural in machines which deal almost always in word (or multiple-word) units, and has the advantage of allowing instructions to use minimally sized fields to contain addresses, which can permit a smaller instruction size or a larger variety of instructions.

When byte processing is to be a significant part of the workload, it is usually more advantageous to use the byte, rather than the word, as the unit of address resolution. Address values which differ by one designate adjacent bytes in memory. This allows an arbitrary character within a character string to be addressed straightforwardly. A word can still be addressed, but the address to be used requires a few more bits than the word-resolution alternative. The word size needs to be an integer multiple of the character size in this organization. This addressing approach was used in the IBM 360, and has been the most common approach in machines designed since then.

When the workload involves processing fields of different sizes, it can be advantageous to address to the bit. Machines with bit addressing may have some instructions that use a programmer-defined byte size and other instructions that operate on fixed data sizes. As an example, on the IBM 7030[4] («Stretch»), a floating point instruction can only address words while an integer arithmetic instruction can specify a field length of 1-64 bits, a byte size of 1-8 bits and an accumulator offset of 0-127 bits.

In a byte-addressable machine with storage-to-storage (SS) instructions, there are typically move instructions to copy one or multiple bytes from one arbitrary location to another. In a byte-oriented (byte-addressable) machine without SS instructions, moving a single byte from one arbitrary location to another is typically:

- LOAD the source byte

- STORE the result back in the target byte

Individual bytes can be accessed on a word-oriented machine in one of two ways. Bytes can be manipulated by a combination of shift and mask operations in registers. Moving a single byte from one arbitrary location to another may require the equivalent of the following:

- LOAD the word containing the source byte

- SHIFT the source word to align the desired byte to the correct position in the target word

- AND the source word with a mask to zero out all but the desired bits

- LOAD the word containing the target byte

- AND the target word with a mask to zero out the target byte

- OR the registers containing the source and target words to insert the source byte

- STORE the result back in the target location

Alternatively many word-oriented machines implement byte operations with instructions using special byte pointers in registers or memory. For example, the PDP-10 byte pointer contained the size of the byte in bits (allowing different-sized bytes to be accessed), the bit position of the byte within the word, and the word address of the data. Instructions could automatically adjust the pointer to the next byte on, for example, load and deposit (store) operations.

Powers of two[edit]

Different amounts of memory are used to store data values with different degrees of precision. The commonly used sizes are usually a power of two multiple of the unit of address resolution (byte or word). Converting the index of an item in an array into the memory address offset of the item then requires only a shift operation rather than a multiplication. In some cases this relationship can also avoid the use of division operations. As a result, most modern computer designs have word sizes (and other operand sizes) that are a power of two times the size of a byte.

Size families[edit]

As computer designs have grown more complex, the central importance of a single word size to an architecture has decreased. Although more capable hardware can use a wider variety of sizes of data, market forces exert pressure to maintain backward compatibility while extending processor capability. As a result, what might have been the central word size in a fresh design has to coexist as an alternative size to the original word size in a backward compatible design. The original word size remains available in future designs, forming the basis of a size family.

In the mid-1970s, DEC designed the VAX to be a 32-bit successor of the 16-bit PDP-11. They used word for a 16-bit quantity, while longword referred to a 32-bit quantity; this terminology is the same as the terminology used for the PDP-11. This was in contrast to earlier machines, where the natural unit of addressing memory would be called a word, while a quantity that is one half a word would be called a halfword. In fitting with this scheme, a VAX quadword is 64 bits. They continued this 16-bit word/32-bit longword/64-bit quadword terminology with the 64-bit Alpha.

Another example is the x86 family, of which processors of three different word lengths (16-bit, later 32- and 64-bit) have been released, while word continues to designate a 16-bit quantity. As software is routinely ported from one word-length to the next, some APIs and documentation define or refer to an older (and thus shorter) word-length than the full word length on the CPU that software may be compiled for. Also, similar to how bytes are used for small numbers in many programs, a shorter word (16 or 32 bits) may be used in contexts where the range of a wider word is not needed (especially where this can save considerable stack space or cache memory space). For example, Microsoft’s Windows API maintains the programming language definition of WORD as 16 bits, despite the fact that the API may be used on a 32- or 64-bit x86 processor, where the standard word size would be 32 or 64 bits, respectively. Data structures containing such different sized words refer to them as:

- WORD (16 bits/2 bytes)

- DWORD (32 bits/4 bytes)

- QWORD (64 bits/8 bytes)

A similar phenomenon has developed in Intel’s x86 assembly language – because of the support for various sizes (and backward compatibility) in the instruction set, some instruction mnemonics carry «d» or «q» identifiers denoting «double-«, «quad-» or «double-quad-«, which are in terms of the architecture’s original 16-bit word size.

An example with a different word size is the IBM System/360 family. In the System/360 architecture, System/370 architecture and System/390 architecture, there are 8-bit bytes, 16-bit halfwords, 32-bit words and 64-bit doublewords. The z/Architecture, which is the 64-bit member of that architecture family, continues to refer to 16-bit halfwords, 32-bit words, and 64-bit doublewords, and additionally features 128-bit quadwords.

In general, new processors must use the same data word lengths and virtual address widths as an older processor to have binary compatibility with that older processor.

Often carefully written source code – written with source-code compatibility and software portability in mind – can be recompiled to run on a variety of processors, even ones with different data word lengths or different address widths or both.

Table of word sizes[edit]

| key: bit: bits, c: characters, d: decimal digits, w: word size of architecture, n: variable size, wm: Word mark | |||||||

|---|---|---|---|---|---|---|---|

| Year | Computer architecture |

Word size w | Integer sizes |

Floatingpoint sizes |

Instruction sizes |

Unit of address resolution |

Char size |

| 1837 | Babbage Analytical engine |

50 d | w | — | Five different cards were used for different functions, exact size of cards not known. | w | — |

| 1941 | Zuse Z3 | 22 bit | — | w | 8 bit | w | — |

| 1942 | ABC | 50 bit | w | — | — | — | — |

| 1944 | Harvard Mark I | 23 d | w | — | 24 bit | — | — |

| 1946 (1948) {1953} |

ENIAC (w/Panel #16[5]) {w/Panel #26[6]} |

10 d | w, 2w (w) {w} |

— | — (2 d, 4 d, 6 d, 8 d) {2 d, 4 d, 6 d, 8 d} |

— — {w} |

— |

| 1948 | Manchester Baby | 32 bit | w | — | w | w | — |

| 1951 | UNIVAC I | 12 d | w | — | 1⁄2w | w | 1 d |

| 1952 | IAS machine | 40 bit | w | — | 1⁄2w | w | 5 bit |

| 1952 | Fast Universal Digital Computer M-2 | 34 bit | w? | w | 34 bit = 4-bit opcode plus 3×10 bit address | 10 bit | — |

| 1952 | IBM 701 | 36 bit | 1⁄2w, w | — | 1⁄2w | 1⁄2w, w | 6 bit |

| 1952 | UNIVAC 60 | n d | 1 d, … 10 d | — | — | — | 2 d, 3 d |

| 1952 | ARRA I | 30 bit | w | — | w | w | 5 bit |

| 1953 | IBM 702 | n c | 0 c, … 511 c | — | 5 c | c | 6 bit |

| 1953 | UNIVAC 120 | n d | 1 d, … 10 d | — | — | — | 2 d, 3 d |

| 1953 | ARRA II | 30 bit | w | 2w | 1⁄2w | w | 5 bit |

| 1954 (1955) |

IBM 650 (w/IBM 653) |

10 d | w | — (w) |

w | w | 2 d |

| 1954 | IBM 704 | 36 bit | w | w | w | w | 6 bit |

| 1954 | IBM 705 | n c | 0 c, … 255 c | — | 5 c | c | 6 bit |

| 1954 | IBM NORC | 16 d | w | w, 2w | w | w | — |

| 1956 | IBM 305 | n d | 1 d, … 100 d | — | 10 d | d | 1 d |

| 1956 | ARMAC | 34 bit | w | w | 1⁄2w | w | 5 bit, 6 bit |

| 1956 | LGP-30 | 31 bit | w | — | 16 bit | w | 6 bit |

| 1957 | Autonetics Recomp I | 40 bit | w, 79 bit, 8 d, 15 d | — | 1⁄2w | 1⁄2w, w | 5 bit |

| 1958 | UNIVAC II | 12 d | w | — | 1⁄2w | w | 1 d |

| 1958 | SAGE | 32 bit | 1⁄2w | — | w | w | 6 bit |

| 1958 | Autonetics Recomp II | 40 bit | w, 79 bit, 8 d, 15 d | 2w | 1⁄2w | 1⁄2w, w | 5 bit |

| 1958 | Setun | 6 trit (~9.5 bits)[b] | up to 6 tryte | up to 3 trytes | 4 trit? | ||

| 1958 | Electrologica X1 | 27 bit | w | 2w | w | w | 5 bit, 6 bit |

| 1959 | IBM 1401 | n c | 1 c, … | — | 1 c, 2 c, 4 c, 5 c, 7 c, 8 c | c | 6 bit + wm |

| 1959 (TBD) |

IBM 1620 | n d | 2 d, … | — (4 d, … 102 d) |

12 d | d | 2 d |

| 1960 | LARC | 12 d | w, 2w | w, 2w | w | w | 2 d |

| 1960 | CDC 1604 | 48 bit | w | w | 1⁄2w | w | 6 bit |

| 1960 | IBM 1410 | n c | 1 c, … | — | 1 c, 2 c, 6 c, 7 c, 11 c, 12 c | c | 6 bit + wm |

| 1960 | IBM 7070 | 10 d[c] | w, 1-9 d | w | w | w, d | 2 d |

| 1960 | PDP-1 | 18 bit | w | — | w | w | 6 bit |

| 1960 | Elliott 803 | 39 bit | |||||

| 1961 | IBM 7030 (Stretch) |

64 bit | 1 bit, … 64 bit, 1 d, … 16 d |

w | 1⁄2w, w | bit (integer), 1⁄2w (branch), w (float) |

1 bit, … 8 bit |

| 1961 | IBM 7080 | n c | 0 c, … 255 c | — | 5 c | c | 6 bit |

| 1962 | GE-6xx | 36 bit | w, 2 w | w, 2 w, 80 bit | w | w | 6 bit, 9 bit |

| 1962 | UNIVAC III | 25 bit | w, 2w, 3w, 4w, 6 d, 12 d | — | w | w | 6 bit |

| 1962 | Autonetics D-17B Minuteman I Guidance Computer |

27 bit | 11 bit, 24 bit | — | 24 bit | w | — |

| 1962 | UNIVAC 1107 | 36 bit | 1⁄6w, 1⁄3w, 1⁄2w, w | w | w | w | 6 bit |

| 1962 | IBM 7010 | n c | 1 c, … | — | 1 c, 2 c, 6 c, 7 c, 11 c, 12 c | c | 6 b + wm |

| 1962 | IBM 7094 | 36 bit | w | w, 2w | w | w | 6 bit |

| 1962 | SDS 9 Series | 24 bit | w | 2w | w | w | |

| 1963 (1966) |

Apollo Guidance Computer | 15 bit | w | — | w, 2w | w | — |

| 1963 | Saturn Launch Vehicle Digital Computer | 26 bit | w | — | 13 bit | w | — |

| 1964/1966 | PDP-6/PDP-10 | 36 bit | w | w, 2 w | w | w | 6 bit 7 bit (typical) 9 bit |

| 1964 | Titan | 48 bit | w | w | w | w | w |

| 1964 | CDC 6600 | 60 bit | w | w | 1⁄4w, 1⁄2w | w | 6 bit |

| 1964 | Autonetics D-37C Minuteman II Guidance Computer |

27 bit | 11 bit, 24 bit | — | 24 bit | w | 4 bit, 5 bit |

| 1965 | Gemini Guidance Computer | 39 bit | 26 bit | — | 13 bit | 13 bit, 26 | —bit |

| 1965 | IBM 1130 | 16 bit | w, 2w | 2w, 3w | w, 2w | w | 8 bit |

| 1965 | IBM System/360 | 32 bit | 1⁄2w, w, 1 d, … 16 d |

w, 2w | 1⁄2w, w, 11⁄2w | 8 bit | 8 bit |

| 1965 | UNIVAC 1108 | 36 bit | 1⁄6w, 1⁄4w, 1⁄3w, 1⁄2w, w, 2w | w, 2w | w | w | 6 bit, 9 bit |

| 1965 | PDP-8 | 12 bit | w | — | w | w | 8 bit |

| 1965 | Electrologica X8 | 27 bit | w | 2w | w | w | 6 bit, 7 bit |

| 1966 | SDS Sigma 7 | 32 bit | 1⁄2w, w | w, 2w | w | 8 bit | 8 bit |

| 1969 | Four-Phase Systems AL1 | 8 bit | w | — | ? | ? | ? |

| 1970 | MP944 | 20 bit | w | — | ? | ? | ? |

| 1970 | PDP-11 | 16 bit | w | 2w, 4w | w, 2w, 3w | 8 bit | 8 bit |

| 1971 | CDC STAR-100 | 64 bit | 1⁄2w, w | 1⁄2w, w | 1⁄2w, w | bit | 8 bit |

| 1971 | TMS1802NC | 4 bit | w | — | ? | ? | — |

| 1971 | Intel 4004 | 4 bit | w, d | — | 2w, 4w | w | — |

| 1972 | Intel 8008 | 8 bit | w, 2 d | — | w, 2w, 3w | w | 8 bit |

| 1972 | Calcomp 900 | 9 bit | w | — | w, 2w | w | 8 bit |

| 1974 | Intel 8080 | 8 bit | w, 2w, 2 d | — | w, 2w, 3w | w | 8 bit |

| 1975 | ILLIAC IV | 64 bit | w | w, 1⁄2w | w | w | — |

| 1975 | Motorola 6800 | 8 bit | w, 2 d | — | w, 2w, 3w | w | 8 bit |

| 1975 | MOS Tech. 6501 MOS Tech. 6502 |

8 bit | w, 2 d | — | w, 2w, 3w | w | 8 bit |

| 1976 | Cray-1 | 64 bit | 24 bit, w | w | 1⁄4w, 1⁄2w | w | 8 bit |

| 1976 | Zilog Z80 | 8 bit | w, 2w, 2 d | — | w, 2w, 3w, 4w, 5w | w | 8 bit |

| 1978 (1980) |

16-bit x86 (Intel 8086) (w/floating point: Intel 8087) |

16 bit | 1⁄2w, w, 2 d | — (2w, 4w, 5w, 17 d) |

1⁄2w, w, … 7w | 8 bit | 8 bit |

| 1978 | VAX | 32 bit | 1⁄4w, 1⁄2w, w, 1 d, … 31 d, 1 bit, … 32 bit | w, 2w | 1⁄4w, … 141⁄4w | 8 bit | 8 bit |

| 1979 (1984) |

Motorola 68000 series (w/floating point) |

32 bit | 1⁄4w, 1⁄2w, w, 2 d | — (w, 2w, 21⁄2w) |

1⁄2w, w, … 71⁄2w | 8 bit | 8 bit |

| 1985 | IA-32 (Intel 80386) (w/floating point) | 32 bit | 1⁄4w, 1⁄2w, w | — (w, 2w, 80 bit) |

8 bit, … 120 bit 1⁄4w … 33⁄4w |

8 bit | 8 bit |

| 1985 | ARMv1 | 32 bit | 1⁄4w, w | — | w | 8 bit | 8 bit |

| 1985 | MIPS I | 32 bit | 1⁄4w, 1⁄2w, w | w, 2w | w | 8 bit | 8 bit |

| 1991 | Cray C90 | 64 bit | 32 bit, w | w | 1⁄4w, 1⁄2w, 48 bit | w | 8 bit |

| 1992 | Alpha | 64 bit | 8 bit, 1⁄4w, 1⁄2w, w | 1⁄2w, w | 1⁄2w | 8 bit | 8 bit |

| 1992 | PowerPC | 32 bit | 1⁄4w, 1⁄2w, w | w, 2w | w | 8 bit | 8 bit |

| 1996 | ARMv4 (w/Thumb) |

32 bit | 1⁄4w, 1⁄2w, w | — | w (1⁄2w, w) |

8 bit | 8 bit |

| 2000 | IBM z/Architecture (w/vector facility) |

64 bit | 1⁄4w, 1⁄2w, w 1 d, … 31 d |

1⁄2w, w, 2w | 1⁄4w, 1⁄2w, 3⁄4w | 8 bit | 8 bit, UTF-16, UTF-32 |

| 2001 | IA-64 | 64 bit | 8 bit, 1⁄4w, 1⁄2w, w | 1⁄2w, w | 41 bit (in 128-bit bundles)[7] | 8 bit | 8 bit |

| 2001 | ARMv6 (w/VFP) |

32 bit | 8 bit, 1⁄2w, w | — (w, 2w) |

1⁄2w, w | 8 bit | 8 bit |

| 2003 | x86-64 | 64 bit | 8 bit, 1⁄4w, 1⁄2w, w | 1⁄2w, w, 80 bit | 8 bit, … 120 bit | 8 bit | 8 bit |

| 2013 | ARMv8-A and ARMv9-A | 64 bit | 8 bit, 1⁄4w, 1⁄2w, w | 1⁄2w, w | 1⁄2w | 8 bit | 8 bit |

| Year | Computer architecture |

Word size w | Integer sizes |

Floatingpoint sizes |

Instruction sizes |

Unit of address resolution |

Char size |

| key: bit: bits, d: decimal digits, w: word size of architecture, n: variable size |

[8][9]

See also[edit]

- Integer (computer science)

Notes[edit]

- ^ Many early computers were decimal, and a few were ternary

- ^ The bit equivalent is computed by taking the amount of information entropy provided by the trit, which is

. This gives an equivalent of about 9.51 bits for 6 trits.

- ^ Three-state sign

References[edit]

- ^ a b Beebe, Nelson H. F. (2017-08-22). «Chapter I. Integer arithmetic». The Mathematical-Function Computation Handbook — Programming Using the MathCW Portable Software Library (1 ed.). Salt Lake City, UT, USA: Springer International Publishing AG. p. 970. doi:10.1007/978-3-319-64110-2. ISBN 978-3-319-64109-6. LCCN 2017947446. S2CID 30244721.

- ^ Dreyfus, Phillippe (1958-05-08) [1958-05-06]. Written at Los Angeles, California, USA. System design of the Gamma 60 (PDF). Western Joint Computer Conference: Contrasts in Computers. ACM, New York, NY, USA. pp. 130–133. IRE-ACM-AIEE ’58 (Western). Archived (PDF) from the original on 2017-04-03. Retrieved 2017-04-03.

[…] Internal data code is used: Quantitative (numerical) data are coded in a 4-bit decimal code; qualitative (alpha-numerical) data are coded in a 6-bit alphanumerical code. The internal instruction code means that the instructions are coded in straight binary code.

As to the internal information length, the information quantum is called a «catena,» and it is composed of 24 bits representing either 6 decimal digits, or 4 alphanumerical characters. This quantum must contain a multiple of 4 and 6 bits to represent a whole number of decimal or alphanumeric characters. Twenty-four bits was found to be a good compromise between the minimum 12 bits, which would lead to a too-low transfer flow from a parallel readout core memory, and 36 bits or more, which was judged as too large an information quantum. The catena is to be considered as the equivalent of a character in variable word length machines, but it cannot be called so, as it may contain several characters. It is transferred in series to and from the main memory.

Not wanting to call a «quantum» a word, or a set of characters a letter, (a word is a word, and a quantum is something else), a new word was made, and it was called a «catena.» It is an English word and exists in Webster’s although it does not in French. Webster’s definition of the word catena is, «a connected series;» therefore, a 24-bit information item. The word catena will be used hereafter.

The internal code, therefore, has been defined. Now what are the external data codes? These depend primarily upon the information handling device involved. The Gamma 60 [fr] is designed to handle information relevant to any binary coded structure. Thus an 80-column punched card is considered as a 960-bit information item; 12 rows multiplied by 80 columns equals 960 possible punches; is stored as an exact image in 960 magnetic cores of the main memory with 2 card columns occupying one catena. […] - ^ Blaauw, Gerrit Anne; Brooks, Jr., Frederick Phillips; Buchholz, Werner (1962). «4: Natural Data Units» (PDF). In Buchholz, Werner (ed.). Planning a Computer System – Project Stretch. McGraw-Hill Book Company, Inc. / The Maple Press Company, York, PA. pp. 39–40. LCCN 61-10466. Archived (PDF) from the original on 2017-04-03. Retrieved 2017-04-03.

[…] Terms used here to describe the structure imposed by the machine design, in addition to bit, are listed below.

Byte denotes a group of bits used to encode a character, or the number of bits transmitted in parallel to and from input-output units. A term other than character is used here because a given character may be represented in different applications by more than one code, and different codes may use different numbers of bits (i.e., different byte sizes). In input-output transmission the grouping of bits may be completely arbitrary and have no relation to actual characters. (The term is coined from bite, but respelled to avoid accidental mutation to bit.)

A word consists of the number of data bits transmitted in parallel from or to memory in one memory cycle. Word size is thus defined as a structural property of the memory. (The term catena was coined for this purpose by the designers of the Bull GAMMA 60 [fr] computer.)

Block refers to the number of words transmitted to or from an input-output unit in response to a single input-output instruction. Block size is a structural property of an input-output unit; it may have been fixed by the design or left to be varied by the program. […] - ^ «Format» (PDF). Reference Manual 7030 Data Processing System (PDF). IBM. August 1961. pp. 50–57. Retrieved 2021-12-15.

- ^ Clippinger, Richard F. [in German] (1948-09-29). «A Logical Coding System Applied to the ENIAC (Electronic Numerical Integrator and Computer)». Aberdeen Proving Ground, Maryland, US: Ballistic Research Laboratories. Report No. 673; Project No. TB3-0007 of the Research and Development Division, Ordnance Department. Retrieved 2017-04-05.

{{cite web}}: CS1 maint: url-status (link) - ^ Clippinger, Richard F. [in German] (1948-09-29). «A Logical Coding System Applied to the ENIAC». Aberdeen Proving Ground, Maryland, US: Ballistic Research Laboratories. Section VIII: Modified ENIAC. Retrieved 2017-04-05.

{{cite web}}: CS1 maint: url-status (link) - ^ «4. Instruction Formats» (PDF). Intel Itanium Architecture Software Developer’s Manual. Vol. 3: Intel Itanium Instruction Set Reference. p. 3:293. Retrieved 2022-04-25.

Three instructions are grouped together into 128-bit sized and aligned containers called bundles. Each bundle contains three 41-bit instruction slots and a 5-bit template field.

- ^ Blaauw, Gerrit Anne; Brooks, Jr., Frederick Phillips (1997). Computer Architecture: Concepts and Evolution (1 ed.). Addison-Wesley. ISBN 0-201-10557-8. (1213 pages) (NB. This is a single-volume edition. This work was also available in a two-volume version.)

- ^ Ralston, Anthony; Reilly, Edwin D. (1993). Encyclopedia of Computer Science (3rd ed.). Van Nostrand Reinhold. ISBN 0-442-27679-6.

Consider the following:

CPU (processor), RAM (main memory), I/O devices (mouse, keyboard, printer), Bus (data transfer component).

How would you like these computer parts to communicate and transfer data?

you definitely need a fixed size of bits to be considered a single unit of data.

For that, Computer scientists agreed to standardize this unit to be 32 bits or 64 bits (depending on the manufacturer choice).

They gave this unit a name and called it a Word.

So a Word is nothing but a unit of data (bunch of bits (signal charges of zeros and ones)) that moves around from a computer component to another.

For instance buses are built with 32 bits (4 bytes) and some with 64 bits (8 bytes). Likewise with the CPU (hardware) and operating systems (software) are built with either 32 bits or 64 bits.

It just happened to be the standard unit named Word and sized 32 bits or 64 bits.

Ps: Word is one of the many data size units that move around inside the computer, different computer components use different sizes to transport data (signals charges that represent zeros and ones), for instance RAM can use size of 64 bits while Buses can use 32 bits. Hardware designers design the architecture of components taking into account these size differences to either implement Word size of 32 bits on only CPU but 64 bits on RAM, or implement the same size on all components, …etc. Word size used to be 8 bits (1 byte), but nowadays the most comment unit size is 64 bits on most computer components such as CPU or RAM, or Bus, …etc.

Word “size” refers to the amount of data a CPU’s internal data registers can hold and process at one time. Modern desktop computers have 64-bit words. Computers embedded in appliances and consumer products have word sizes of 8, 16 or 32 bits. See bit and byte.

Contents

- 1 What is the word size of a computer measured in?

- 2 What is the size of each word?

- 3 Is a word 16 or 32 bits?

- 4 What is a word in computers?

- 5 What is the word size of a 64 bit computer?

- 6 Why is a computer word size important?

- 7 How do you find a word size?

- 8 What is digital word?

- 9 What do you mean by 32 bit or 64-bit word size?

- 10 What is 64-bit system?

- 11 What are the speed and word size of the CPU?

- 12 What is word in C?

- 13 What is word size in RAM?

- 14 How much is a word size?

- 15 How do I know 64-bit or 32-bit?

- 16 What is word size of a processor?

- 17 What is the effect of word size on processor speed?

- 18 What are the 7 types of computers?

- 19 What is the word size of 32 GB RAM?

- 20 Is digitally a real word?

What is the word size of a computer measured in?

“Word size” refers to the number of bits processed by a computer’s CPU in one go (these days, typically 32 bits or 64 bits).

What is the size of each word?

A byte is eight bits, a word is 2 bytes (16 bits), a doubleword is 4 bytes (32 bits), and a quadword is 8 bytes (64 bits).

Is a word 16 or 32 bits?

In x86 assembly language WORD , DOUBLEWORD ( DWORD ) and QUADWORD ( QWORD ) are used for 2, 4 and 8 byte sizes, regardless of the machine word size. A word is typically the “native” data size of the CPU. That is, on a 16-bit CPU, a word is 16 bits, on a 32-bit CPU, it’s 32 and so on.

What is a word in computers?

In computer architecture, a word is a unit of data of a defined bit length that can be addressed and moved between storage and the computer processor.A word can contain a computer instruction, a storage address, or application data that is to be manipulated (for example, added to the data in another word space).

What is the word size of a 64 bit computer?

Each set of 8 bits is called a byte. Two bytes together as in a 16 bit machine make up a word , 32 bit machines are 4 bytes which is a double word and 64 bit machines are 8 bytes which is a quad word.

Why is a computer word size important?

Explanation: The word size of a computer generally indicates the largest integer it can process in a single instruction, and the size of a memory address, which is usually, but not necessarily the same as the integer size. The main indication of the word size is how much memory the processor can address.

How do you find a word size?

That being said, on Windows with Intel processors, the nominal word size will be either 32 or 64 bits and you can easily figure this out:

- if your program is compiled for 32-bits, then the nominal word size is 32-bits.

- if you have compiled a 64-bit program then then the nominal word size is 64-bits.

What is digital word?

1 : relating to or using calculation directly with digits rather than through measurable physical quantities. 2 : of or relating to data in the form of numerical digits digital images digital broadcasting. 3 : providing displayed or recorded information in numerical digits from an automatic device a digital watch.

What do you mean by 32 bit or 64-bit word size?

Traditionally the term “word” refers to the size of the processor’s registers and main data path. By that definition a “word” would be 32 bit on your 32-bit system and 64-bit on your 64-bit system.

What is 64-bit system?

An operating system that is designed to work in a computer that processes 64 bits at a time.A 64-bit operating system will not work in a 32-bit computer, but a 32-bit operating system will run in a 64-bit computer. See 64-bit computing.

What are the speed and word size of the CPU?

(1) The word size for a computer is the number of bits that the central processing unit (CPU) of a particular computer can handle at one time. These word sizes range from a nibble to more than 128 bits. (2) Word size = 16 bits (or two bytes).

A word is an integer number of bytes for example, one, two, four, or eight. When someone talks about the “n-bits” of a machine, they are generally talking about the machine’s word size. For example, when people say the Pentium is a 32-bit chip, they are referring to its word size, which is 32 bits, or four bytes.

What is word size in RAM?

Traditionally, a “word” in computer architectures was generally the smallest addressable unit of memory. And traditionally this has been the same as the machine’s general purpose register size.

How much is a word size?

Word “size” refers to the amount of data a CPU’s internal data registers can hold and process at one time. Modern desktop computers have 64-bit words. Computers embedded in appliances and consumer products have word sizes of 8, 16 or 32 bits.

How do I know 64-bit or 32-bit?

Press and hold the Windows key and the Pause key. In the System window, next to System type, it lists 32-bit Operating System for a 32-bit version of Windows, and 64-bit Operating System if you’re running the 64-bit version.

What is word size of a processor?

A word is a fixed-sized piece of data handled as a unit by the instruction set or the hardware of the processor.Modern processors, including embedded systems, usually have a word size of 8, 16, 24, 32, or 64 bits, while modern general purpose computers usually use 32 or 64 bits.

What is the effect of word size on processor speed?

On the x86 processors (so this is what happens on all modern PC and Mac), for historical reasons, the 64-bit mode does not come only with 64-bit registers; it also offers twice as many registers to the application, and this helps performance by a fair bit.

What are the 7 types of computers?

Types of computers

- Supercomputer.

- Mainframe.

- Server Computer.

- Workstation Computer.

- Personal Computer or PC.

- Microcontroller.

- Smartphone. 8 References.

What is the word size of 32 GB RAM?

A 32bit CPU will have a 32bit word, a 64bit CPU will deal with 64bit words.

Is digitally a real word?

Yes, digitally is in the scrabble dictionary.

Table of Contents

About

Articles Related

Management

Values

The size of a word is CPU-specific.

-

6,

-

12,

-

16,

-

18,

-

24,

-

a 32-bit computer (4 bytes)

-

36,

-

39,

-

40,

-

48,

-

60,

-

a 64-bit computer (8 bytes)

The computing world is in transition from 8 bit, to 16 bit, to 32-bit to 64-bit computers.

Show

Limitation

The only limitation imposed is by the 32-bit or 64-bit mode of the process.

-

A 64-bit OS can execute both 32-bit and 64-bit programs as the 64-bit mode is an upward extension of 32-bit mode.

-

A 32-bit OS can only execute 32-bit programs.

Documentation / Reference

Recommended Pages

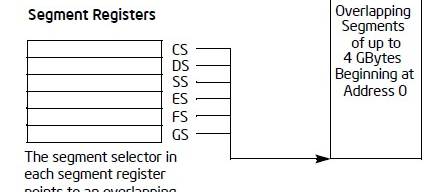

Memory Segment — Segment Register

Memory Segment — Segment Register

About

The segment registers (CS, DS, SS, ES, FS, and GS) hold 16-bit segment selectors

To access a particular segment in memory, the segment selector for that segm «…

Memory — (Primary|Main|Internal) Memory

Main memory is also known as: Primary storage internal memory (to distinguish from external memory, such as hard drives) often referred to simply as memory, is the only one directly accessible to th «…

Computer — Central processing unit (CPU)

Computer — Central processing unit (CPU)

About

A CPU is just a device name that indicate a device that controls a computer system.

A CPU is also known as:

* a

* or

The fundamental operation «…

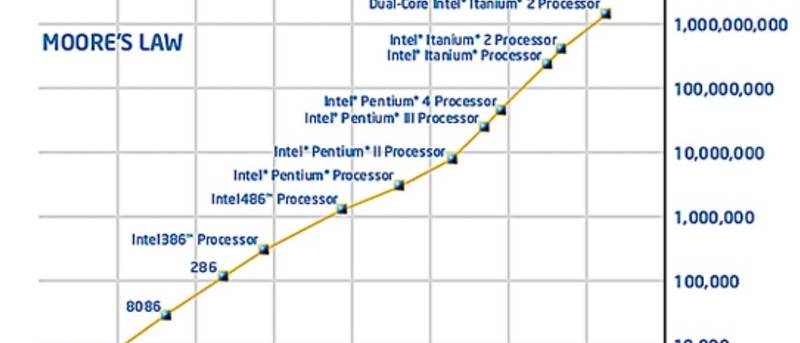

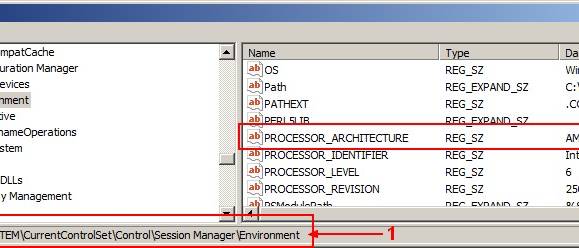

Windows — Cpu (Instruction Set Architecture and word size — 32 or 64 Bit)

Windows — Cpu (Instruction Set Architecture and word size — 32 or 64 Bit)

About

in Windows showing particularly:

* the

* and

word size

* a 64 bit

* and a 32 bit

* registry key

«…

32 bits long word

32 bits long word

64 bits long word

64 bits long word

Assembly — The Netwide Assembler (nasm)

nasm is an assembler that will compile assembly code in machine instruction. Articles Related Syntax . More see

Utility where: -f option speci «…

Byte (Bit Octet) — Computer storage Unit

(8bit) The byte is the smallest unit of computer storage and represents: 8 bits. or 2 hexadecimal (1 hexa = 4 bit) Computer storage capacity is measured in bytes. In today’s large-capacity serve «…

CPU — Linux

CPU in a Linux context How to get information on the CPU ? lscpu where: x86_64 means: a X86 architecture with a 64 bit word size cpuinfo 1 block of information by core You can see the cpu cache Qu «…

CPU — Word

A word is a fixed-sized piece of data processed as a unit by the processor. The word size is defined in the instruction set architecture. The term word is used for a small group of bits that are handl «…

What Does Word Size Mean?

In computing, word size refers to the maximum number of bits that a CPU can process at a time. A word is a fixed-sized piece of data which is dictated by the processor hardware architecture; fixed in a sense that it is the maximum size that the processor is always using, yet variable in the sense that word sizes vary amongst processor architectures, most notably because of generation and the state of technology.

Techopedia Explains Word Size

Word size has varied in size and even in meaning throughout the history of the computer. Originally, “word” meant 16 bits, as that was the maximum possible value at the time. But as processor hardware technology progressed and computers were able to handle larger and larger amounts of data, word simply became the maximum possible number of bits that the processor in question can process. So word size could be as low as 4 bits or as high as 64 bits, depending on what a particular processor can handle.

Word size is used for a number of concepts, all relating to processing. It is used in any of the following:

- Addresses — The address must be able to represent the full range possible, so it uses a full word or a multiple of it.

- Fixed-point numbers — Integers are available in different sizes, but usually it takes the size of the full word supported by the processor.

- Floating-point numbers — Holders for floating-point numbers typically use the full word size length or multiples of it.

- Registers — The size of the register depends on the kind of register and what its purpose is, but a general-purpose register usually uses the maximum word size capability of the processor.

- Instructions — Instruction sets for processors are often coded in full word size.

A word is a set number of bits managed as a unit.

Contents

- 1 Hardware Word

- 2 Common Names for Various Word Sizes

- 2.1 Bit

- 2.2 Byte

- 2.3 Octet

- 2.4 Nibble

- 2.5 Half word, Single word, Double word, Quad word

Hardware Word

A hardware word is the group of bits normally managed by a processor. The word size is a distinguishing feature of a processor, and is typically a power-of-two multiple of eight bits (8, 16, 32, or 64 bits), although some rare or early processors used different word sizes.

The word size is usually associated with the size of general-purpose registers and the amount of data read from or written to memory at one time. Most modern processors can read/write alternate word sizes (for example, a «64-bit» x86_64 system can also read/write 32, 16, and 8 bit values to/from memory, and 64-bit registers can be accessed as 32, 16, or 8-bit subsets). Additionally, many modern systems use a different memory word size than CPU word size (for example, a «64-bit» system may be built to read/write memory 128 bits at a time), but this is transparent to the programmer and user.

Common Names for Various Word Sizes

Bit

A bit is a single binary digit, a value that can take one of two states. These states may be referred to as:

- 1 or 0

- True or False

- On or Off (electrically)

- Positive or Negative charge, or Forward or Reverse current flow (electrically — differential signalling)

Byte

A byte is a collection of eight bits. It is a convenient size for use with many small character sets such as ASCII, ISO8859, and EBCDIC, and can also be used with the UTF-8 encoding of Unicode. It is often viewed as the smallest hardware word size that makes sense for general-purpose computing.

Most computers with larger hardware word sizes continue to rank memory, storage, and data sizes in bytes (or prefixed multiples of bytes) for comparability. For example, an x86_64 system will be advertised as having «16 gigabytes» of memory instead of «2 gigawords».

Octet

Another name for byte, commonly used in telecommunication standards and in French.

Nibble

A nibble (or nybble) is a half-byte, corresponding to one hexadecimal or BCD digit.

Half word, Single word, Double word, Quad word

The terms half word (or halfword or half-word), single word, double word, and quad word are often used in contemporary computing to refer to common word sizes relative to a 32-bit base word size:

- half word = 16 bits

- single word = 32 bits

- double word = 64 bits

- quad word = 128 bits

This terminology can be seen, for example, in the lane naming conventions for AArch64 SIMD (where v0.8h refers to the 128-bit vector register 0 divided in eight half word lanes) and x86_86 instruction suffixes (MOVQ to move a quad word).

The 32-bit base size is reflective of the 32-bit standard integer size used in the predominant LP64 (and less common ILP32) programming models.

Read this article. As it explains:

«In computing, a word is the natural unit of data used by a particular processor design. A word is a fixed-sized piece of data handled as a unit by the instruction set or the hardware of the processor. The number of bits in a word (the word size, word width, or word length) is an important characteristic of any specific processor design or computer architecture.»

In computing, a word is the natural unit of data used by a particular processor design. A word is a fixed-sized piece of data handled as a unit by the instruction set or the hardware of the processor. The number of bits in a word (the word size, word width, or word length) is an important characteristic of any specific processor design or computer architecture.

The size of a word is reflected in many aspects of a computer’s structure and operation; the majority of the registers in a processor are usually word sized and the largest piece of data that can be transferred to and from the working memory in a single operation is a word in many (not all) architectures. The largest possible address size, used to designate a location in memory, is typically a hardware word (here, «hardware word» means the full-sized natural word of the processor, as opposed to any other definition used).

Modern processors, including embedded systems, usually have a word size of 8, 16, 24, 32, or 64 bits, while modern general purpose computers usually use 32 or 64 bits. Special purpose digital processors, such as DSPs for instance, may use other sizes, and many other sizes have been used historically, including 9, 12, 18, 24, 26, 36, 39, 40, 48, and 60 bits. The slab is an example of a system with an earlier word size. Several of the earliest computers (and a few modern as well) used BCD rather than plain binary, typically having a word size of 10 or 12 decimal digits, and some early decimal computers had no fixed word length at all.

The size of a word can sometimes differ from the expected due to backward compatibility with earlier computers. If multiple compatible variations or a family of processors share a common architecture and instruction set but differ in their word sizes, their documentation and software may become notationally complex to accommodate the difference (see Size families below).

Uses of words

Depending on how a computer is organized, word-size units may be used for:

- Fixed point numbers

- Holders for fixed point, usually integer, numerical values may be available in one or in several different sizes, but one of the sizes available will almost always be the word. The other sizes, if any, are likely to be multiples or fractions of the word size. The smaller sizes are normally used only for efficient use of memory; when loaded into the processor, their values usually go into a larger, word sized holder.

- Floating point numbers

- Holders for floating point numerical values are typically either a word or a multiple of a word.

- Addresses

- Holders for memory addresses must be of a size capable of expressing the needed range of values but not be excessively large, so often the size used is the word though it can also be a multiple or fraction of the word size.

- Registers

- Processor registers are designed with a size appropriate for the type of data they hold, e.g. integers, floating point numbers or addresses. Many computer architectures use «general purpose registers» that can hold any of several types of data, these registers must be sized to hold the largest of the types, historically this is the word size of the architecture though increasingly special purpose, larger, registers have been added to deal with newer types.

- Memory-processor transfer

- When the processor reads from the memory subsystem into a register or writes a register’s value to memory, the amount of data transferred is often a word. Historically, this amount of bits which could be transferred in one cycle was also called a catena in some environments (such as the Bull GAMMA 60 (fr)). In simple memory subsystems, the word is transferred over the memory data bus, which typically has a width of a word or half-word. In memory subsystems that use caches, the word-sized transfer is the one between the processor and the first level of cache; at lower levels of the memory hierarchy larger transfers (which are a multiple of the word size) are normally used.

- Unit of address resolution

- In a given architecture, successive address values designate successive units of memory; this unit is the unit of address resolution. In most computers, the unit is either a character (e.g. a byte) or a word. (A few computers have used bit resolution.) If the unit is a word, then a larger amount of memory can be accessed using an address of a given size at the cost of added complexity to access individual characters. On the other hand, if the unit is a byte, then individual characters can be addressed (i.e. selected during the memory operation).

- Instructions

- Machine instructions are normally the size of the architecture’s word, such as in RISC architectures, or a multiple of the «char» size that is a fraction of it. This is a natural choice since instructions and data usually share the same memory subsystem. In Harvard architectures the word sizes of instructions and data need not be related, as instructions and data are stored in different memories; for example, the processor in the 1ESS electronic telephone switch had 37-bit instructions and 23-bit data words.

Word size choice

When a computer architecture is designed, the choice of a word size is of substantial importance. There are design considerations which encourage particular bit-group sizes for particular uses (e.g. for addresses), and these considerations point to different sizes for different uses. However, considerations of economy in design strongly push for one size, or a very few sizes related by multiples or fractions (submultiples) to a primary size. That preferred size becomes the word size of the architecture.

Character size was in the past (pre-variable-sized character encoding) one of the influences on unit of address resolution and the choice of word size. Before the mid-1960s, characters were most often stored in six bits; this allowed no more than 64 characters, so the alphabet was limited to upper case. Since it is efficient in time and space to have the word size be a multiple of the character size, word sizes in this period were usually multiples of 6 bits (in binary machines). A common choice then was the 36-bit word, which is also a good size for the numeric properties of a floating point format.

After the introduction of the IBM System/360 design, which used eight-bit characters and supported lower-case letters, the standard size of a character (or more accurately, a byte) became eight bits. Word sizes thereafter were naturally multiples of eight bits, with 16, 32, and 64 bits being commonly used.

Variable word architectures

Early machine designs included some that used what is often termed a variable word length. In this type of organization, a numeric operand had no fixed length but rather its end was detected when a character with a special marking, often called word mark, was encountered. Such machines often used binary coded decimal for numbers. This class of machines included the IBM 702, IBM 705, IBM 7080, IBM 7010, UNIVAC 1050, IBM 1401, and IBM 1620.

Most of these machines work on one unit of memory at a time and since each instruction or datum is several units long, each instruction takes several cycles just to access memory. These machines are often quite slow because of this. For example, instruction fetches on an IBM 1620 Model I take 8 cycles just to read the 12 digits of the instruction (the Model II reduced this to 6 cycles, or 4 cycles if the instruction did not need both address fields). Instruction execution took a completely variable number of cycles, depending on the size of the operands.

Word and byte addressing

The memory model of an architecture is strongly influenced by the word size. In particular, the resolution of a memory address, that is, the smallest unit that can be designated by an address, has often been chosen to be the word. In this approach, address values which differ by one designate adjacent memory words. This is natural in machines which deal almost always in word (or multiple-word) units, and has the advantage of allowing instructions to use minimally sized fields to contain addresses, which can permit a smaller instruction size or a larger variety of instructions.

When byte processing is to be a significant part of the workload, it is usually more advantageous to use the byte, rather than the word, as the unit of address resolution. This allows an arbitrary character within a character string to be addressed straightforwardly. A word can still be addressed, but the address to be used requires a few more bits than the word-resolution alternative. The word size needs to be an integer multiple of the character size in this organization. This addressing approach was used in the IBM 360, and has been the most common approach in machines designed since then.

Individual bytes can be accessed on a word-oriented machine in one of two ways. Bytes can be manipulated by a combination of shift and mask operations in registers. Moving a single byte from one arbitrary location to another may require the equivalent of the following:

- LOAD the word containing the source byte

- SHIFT the source word to align the desired byte to the correct position in the target word

- AND the source word with a mask to zero out all but the desired bits

- LOAD the word containing the target byte

- AND the target word with a mask to zero out the target byte

- OR the registers containing the source and target words to insert the source byte

- STORE the result back in the target location

Alternatively many word-oriented machines implement byte operations with instructions using special byte pointers in registers or memory. For an example the PDP-10 byte pointer contained the size of the byte in bits (allowing different-sized bytes to be accessed), the bit position of the byte within the word, and the word address of the data. Instructions could automatically adjust the pointer to the next byte on, for example, load and deposit (store) operations.

Powers of two

Different amounts of memory are used to store data values with different degrees of precision. The commonly used sizes are usually a power of two multiple of the unit of address resolution (byte or word). Converting the index of an item in an array into the address of the item then requires only a shift operation rather than a multiplication. In some cases this relationship can also avoid the use of division operations. As a result, most modern computer designs have word sizes (and other operand sizes) that are a power of two times the size of a byte.

Size families

As computer designs have grown more complex, the central importance of a single word size to an architecture has decreased. Although more capable hardware can use a wider variety of sizes of data, market forces exert pressure to maintain backward compatibility while extending processor capability. As a result, what might have been the central word size in a fresh design has to coexist as an alternative size to the original word size in a backward compatible design. The original word size remains available in future designs, forming the basis of a size family.

In the mid-1970s, DEC designed the VAX to be a successor of the PDP-11. They used word for a 16-bit quantity, while longword referred to a 32-bit quantity. This was in contrast to earlier machines, where the natural unit of addressing memory would be called a word, while a quantity that is one half a word would be called a halfword. In fitting with this scheme, a VAX quadword is 64 bits.

Another example is the x86 family, of which processors of three different word lengths (16-bit, later 32- and 64-bit) have been released. As software is routinely ported from one word-length to the next, some APIs and documentation define or refer to an older (and thus shorter) word-length than the full word length on the CPU that software may be compiled for. Also, similar to how bytes are used for small numbers in many programs, a shorter word (16 or 32 bits) may be used in contexts where the range of a wider word is not needed (especially where this can save considerable stack space or cache memory space). For example, Microsoft’s Windows API maintains the programming language definition of WORD as 16 bits, despite the fact that the API may be used on a 32- or 64-bit x86 processor, where the standard word size would be 32 or 64 bits, respectively. Data structures containing such different sized words refer to them as WORD (16 bits/2 bytes), DWORD (32 bits/4 bytes) and QWORD (64 bits/8 bytes) respectively. A similar phenomenon has developed in Intel’s x86 assembly language – because of the support for various sizes (and backward compatibility) in the instruction set, some instruction mnemonics carry «d» or «q» identifiers denoting «double-«, «quad-» or «double-quad-«, which are in terms of the architecture’s original 16-bit word size.

In general, new processors must use the same data word lengths and virtual address widths as an older processor to have binary compatibility with that older processor.

Often carefully written source code – written with source code compatibility and software portability in mind – can be recompiled to run on a variety of processors, even ones with different data word lengths or different address widths or both.

Source: Wikipedia, https://en.wikipedia.org/wiki/Word_(computer_architecture)

You should upgrade or use an alternative browser.

-

Forums

-

Engineering

-

Electrical Engineering

What is the word size of a processor?

-

Thread starter

treehouse -

Start date

Sep 4, 2011

- Sep 4, 2011

- #1

Answers and Replies

- Sep 4, 2011

- #2

It is NOT, by the way, the fundamental MEMORY structure size. That’s the byte. These days folks think «byte = 8 bits» but that’s not correct. There are mainframe processors where the byte size = the word size = 32 bits. On PCs the byte IS 8 bits, but it’s not defined as 8 bits. The problem, to the extent that one can consider it a problem, of having a byte size smaller than a word size is that it then requires multiple memory fetches to get a word for processing. That’s why mainframes (think FAST) often have byte size = word size.

- Sep 4, 2011

- #3

My knowledge is in the grandfather’s days, but I really think the word is defined as 16 bit just like the byte is 8 bits and never change! Today when they talk about 64 bit bus is 4 word wide! Correct me if I am wrong as I am an analog guy that over step into the digital world.

- Sep 4, 2011

- #4

I don’t know what elaboration it needs. That’s it. It is the organizational structure size of the processor. It’s how big the registers are. It’s how wide the ALU is. It is, as you said, the # of bits a processor can process at one time.It is NOT, by the way, the fundamental MEMORY structure size. That’s the byte. These days folks think «byte = 8 bits» but that’s not correct. There are mainframe processors where the byte size = the word size = 32 bits. On PCs the byte IS 8 bits, but it’s not defined as 8 bits. The problem, to the extent that one can consider it a problem, of having a byte size smaller than a word size is that it then requires multiple memory fetches to get a word for processing. That’s why mainframes (think FAST) often have byte size = word size.

For the ALU, register, and the processor itself, how is the word size physically expressed?

- Sep 4, 2011

- #5

I thought word is 16bits and has nothing to do with how many bits the processor can process at one time.My knowledge is in the grandfather’s days, but I really think the word is defined as 16 bit just like the byte is 8 bits and never change! Today when they talk about 64 bit bus is 4 word wide! Correct me if I am wrong as I am an analog guy that over step into the digital world.

That is incorrect. My post is correct. I’ve been doing and teaching this stuff since 1962.

- Sep 4, 2011

- #6

For the ALU, register, and the processor itself, how is the word size physically expressed?

As a number. For the Z80 and early Intel processors (8080) it was 8 bits.

For mini-computers in the 1970’s it was 16 bits.

For some mainframes it has been various values. I’ve seen 32, 64, 66 and I vaguely recall one that I think had 80 bits. Very weird.

When computers have bytes size less than word size, then, as I said, it requires multiple fetches for a word to process. Actual physical fetching is often augmented by various schemes to avoid too much slowdown, and pipelines are often used for the same reason. Only when the instruction path changes (a jump instruction) does the pipeline have to be dumped and restarted for instruction fetches. Data fetches are more likely to be random so often can’t avoid the slowdown.

- Sep 4, 2011

- #7

As a number. For the Z80 and early Intel processors (8080) it was 8 bits.For mini-computers in the 1970’s it was 16 bits.

For some mainframes it has been various values. I’ve seen 32, 64, 66 and I vaguely recall one that I think had 80 bits. Very weird.

When computers have bytes size less than word size, then, as I said, it requires multiple fetches for a word to process. Actual physical fetching is often augmented by various schemes to avoid too much slowdown, and pipelines are often used for the same reason. Only when the instruction path changes (a jump instruction) does the pipeline have to be dumped and restarted for instruction fetches. Data fetches are more likely to be random so often can’t avoid the slowdown.

I really enjoyed reading your post, phinds. Thanks.

I’ll remember most of the terminology but I won’t really understand it without further elaboration.

- Sep 5, 2011

- #8

- Sep 5, 2011

- #9

As I recall, a nibble is 4 bits — a chunk size taken because the value it holds it can be expressed with one hex «digit».

Don’t know if that was ever «formally» defined, but I’ve seen it used a lot as meaning 4 bits. The name, obviously, is chosen because it is part of a byte, not a whole «bite».

- Sep 5, 2011

- #10

I really enjoyed reading your post, phinds. Thanks.

I’ll remember most of the terminology but I won’t really understand it without further elaboration.

Hm … I’m not clear on what further elaboration you need here. Can you be more specific? What exactly is it that doesn’t quite sink in? Can you even pinpoint it? (I know I sometimes have a hard time figuring out just what something won’t stick with me).

- Sep 5, 2011

- #11

Hm … I’m not clear on what further elaboration you need here. Can you be more specific? What exactly is it that doesn’t quite sink in? Can you even pinpoint it? (I know I sometimes have a hard time figuring out just what something won’t stick with me).

I want to know how it is that each word is read individually.

- Sep 5, 2011

- #12

As I recall, a nibble is 4 bits — a chunk size taken because the value it holds it can be expressed with one hex «digit».Don’t know if that was ever «formally» defined, but I’ve seen it used a lot as meaning 4 bits. The name, obviously, is chosen because it is part of a byte, not a whole «bite».

That’s what I would have said, too — just checking that we are both on the same hymn sheet. But I have never heard of a Byte as being anything other than 8bits. ‘Words’ have always, to me, contained a certain number of Bytes- e.g. «a four Byte word», with 32bits. I haven’t ever seen a Byte being specifically (re?)defined at the beginning of any text, which would be necessary if it could ever be taken as other than 8 bits.

I still have a ‘facts’ booklet (July 1966) for an Elliott 803 computer which used 19 and 39 bit words, with 5 hole punched paper tape and 35mm sound film as the bulk storage medium. Moreover, the instructions were specified in Octal. There is no mention of the word «Byte» in the whole booklet. A real blast from the past. The department soon got into DEC mini computers and then the Byte appeared over my horizon. Amazing that this long word architecture went away, only to come back again.

- Sep 5, 2011

- #13

I want to know how it is that each word is read individually.

Most off the shelf memory basically uses 8bit storage. For the processor to use it, it is necessary to take the data out in four, 8 or any other number of dollops. This is done by what I think they call a Memory Chip Controller which, I guess, assembles data from a number of different locations. This presents the processor with already- assembled words, saving it a lot of time.

This really isn’t the place to go into the details of computer design — you need a big book and a hot towel for this, I think! Beware all the jargon and acronyms.

- Sep 5, 2011

- #14

Most off the shelf memory basically uses 8bit storage. For the processor to use it, it is necessary to take the data out in four, 8 or any other number of dollops. This is done by what I think they call a Memory Chip Controller which, I guess, assembles data from a number of different locations. This presents the processor with already- assembled words, saving it a lot of time.This really isn’t the place to go into the details of computer design — you need a big book and a hot towel for this, I think! Beware all the jargon and acronyms.

I agree w/ all of that, BUT … mainframes, at least the early ones, did not use 8-bit chunks. The byte was the same as the word … generally 32 bits, but sometimes more, and mini-computers also did not use 8 bit chunks, the byte was the same as the word (16 bits). I don’t know what modern mainframes use.

I can’t put my hands on a formal definition of «byte» but I recall from my early days, it WAS specifically defined as «the smallest addressable chunk of memory» and over time, as that quantity settled in on 8 bits for computers that most of the world is familiar with, «byte» came to take on the de facto meaning of 8 bits and I have had folks argue w/ me vehemently that it IS ONLY 8 BITS.

treehouse, let me add this about the architecture:

A computer has what’s called a CPU (central processing unit), an ALU (arithmetic/logic unit) and an MAR (memory address register), among other things. The MAR is filled with a memory address and the fetch electronics gets the contents of that address. If the byte size is smaller than the word size, then multiple fetches are performed. This fills up a register in the CPU with the contents of memory. If that is an instruction, it goes to the instruction decoding register which has a whole ton of logic on its output to decipher the instruction and do stuff. If it’s a data value, it goes to the ALU (or possibly to a specific register if so directed) where it can be used in subsequenst data manipulations.

It’s not really as complicted as it might sound and it’s tons of fun to learn, but as sophiecentaur, you DO need a big book and a hot towel (I would have said headache pills) because even though it’s fun, it does get a bit weird until you get it all down in your head.

- Sep 5, 2011

- #15

The 803 was the nearest I came to actual computer hardware in those days. I don’t think they had even heard of the word.

- Sep 5, 2011

- #16

Ah. I see we are using the Anglo Saxon version of ye worde Byte. lol

The 803 was the nearest I came to actual computer hardware in those days. I don’t think they had even heard of the word.

Actually, as I recall, the word byte really was NOT used much at all in the early days, as it was really only of interest to us specialists. I don’t think programmers, for example, used it. I designed computer hardware so was heavily into hardware architecture. I think it was only with the advent of personal computers that it started being used and because they all used an 8-bit byte, people started early on in the PC era to use the word as synonymous with 8 bits.

- Sep 5, 2011

- #17

- Sep 5, 2011

- #18

It is the organizational structure size of the processor. It’s how big the registers are. It’s how wide the ALU is. It is, as you said, the # of bits a processor can process at one time.

there are a few things correct about what phinds sez here and a few things that are not. if we’re referring to a generic processor, the registers inside may be of different widths. some registers may be twice as wide as others.

it also matters what data one is referring to. some DSP and RISC chips have opcode word size that is larger than the data word size.

the most consistent definition that is accurate in a wide variety of situations is the word size of a processor is the the width of the ALU (arithmetic logic unit). this is not always the number of bits that the processor processes «at a time». some embedded chips may have an internal ALU word of 32 bits, but have a data bus width of 8 bits, so the chip has to access four 8-bit words (at different times at the nanosecond scale) before it can process them.

i, personally, like it if a chip has ALU width, data bus width, address bus width, and opcode width all of the same width. i really hate fiddling with efficiently stuffing 48-bit opcodes into 32-bit wide memory spaces.

It is NOT, by the way, the fundamental MEMORY structure size. That’s the byte. These days folks think «byte = 8 bits» but that’s not correct. There are mainframe processors where the byte size = the word size = 32 bits. On PCs the byte IS 8 bits, but it’s not defined as 8 bits. The problem, to the extent that one can consider it a problem, of having a byte size smaller than a word size is that it then requires multiple memory fetches to get a word for processing. That’s why mainframes (think FAST) often have byte size = word size.

phinds, your knowledge is anachronistic. nowadays, nearly a half century from 1962, if you buy or spec any chip, hard drive, thumb drive, blank CD, or whatever storage device, and if the memory capacity is expressed in «bytes» (often they spec it in bits), after any 8-to-6 (or whatever) coding scheme, the number of bits of storage available to the user is always 8 times the number of bytes that the spec. that is always the case and if phinds thinks differently, his knowledge of usage of the word is a few decades out of date.

to his (or her) credit:

from wikipedia:

The size of the byte has historically been hardware dependent and no definitive standards exist that mandate the size. The de facto standard of eight bits is a convenient power of two permitting the values 0 through 255 for one byte. Many types of applications use variables representable in eight or fewer bits, and processor designers optimize for this common usage. The popularity of major commercial computing architectures have aided in the ubiquitous acceptance of the 8-bit size.

note the term «ubiquitous acceptance».

- Sep 5, 2011

-

- #19

What architecture makes it such that the word size is all that is processed at a time?

I don’t think you are going to get a suitable answer here, to be honest. Some of us are taking trips down memory lane and others of us are in the modern day. What you need is to look all this up (there must be thousands of books that are good enough to make a start with — or even Wiki). The whole business of computer architecture is far too complicated for a ‘question and answer’ method of learning. I / we have no idea of how much you actually know so any answers can’t be tailored to your needs, I fear. You could waste a lot of your own time trying to do it this way.

Specific and not open questions are better suited to this sort of forum.

- Sep 5, 2011

- #20

I agree that 8 bits is the de facto std for «byte» (and folks now would think it wrong to use it any other way) but as the wiki points out, that’s not really the definition.

- Sep 5, 2011

- #21

Another one: «If they go back to the processor, how are they specially incorporated as a result of coming from the register?»

- Sep 5, 2011

- #22

This whole thread is getting bogged down in your asking simple-sounding questions that have answers that are a bit more complex than you realize and not subject to simple answers. I second the original suggestion that you drop this Q&A attempt to learn computer architecture and get some written material and read it. It isn’t all THAT complicated, but it IS more complicated than is suitable for this kind of Q&A

Suggested for: What is the word size of a processor?

- Jul 6, 2022

- Aug 11, 2022

- Mar 7, 2022

- Nov 10, 2022

- Sep 11, 2020

- Mar 5, 2021

- Dec 13, 2022

- Sep 21, 2021

- Dec 7, 2021

- Oct 22, 2021

-

Forums

-

Engineering

-

Electrical Engineering

I did lot of research on internet but couldn’t get my answer. I want to know what is the difference between the word size and CPU architecture?

For eg.- I read that CPU of 32-bit architecture can address 2^32 memory locations. Now if we consider that one address points to a single byte, then it means we can have memory size of 2^32 Bytes. We can call it byte addressable memory.

Now, I also read that word size is the size of register in a CPU, i.e., it is the minimum no. of bits on which a CPU works upon.

So, help me understand here what is the word size of this computer organization? Is it 32-bit or 1 Byte (as memory is byte addressable)?

What if one address could point 2 Bytes of data instead of 1 Byte? What would be word size then?

Consider the following link.

GATE CS Questions on computer organisation

Question no. 3 from this link is as follows-

A machine has a 32-bit architecture, with 1-word long instructions. It has 64 registers, each of which is 32 bits long. It needs to support 45 instructions, which have an immediate operand in addition to two register operands. Assuming that the immediate operand is an unsigned integer, the maximum value of the immediate operand is

Now, the very first line of the solution says-

As machine has 32-bit architecture, therefore, 1 word = 32 bits = instruction size

How can we say that since CPU is 32-bit, word size is also 32 bit. Doesn’t 32-bit architecture just mean that the no. of addresses in the physical memory is 2^32? And also doesn’t the word size mean the size of memory each of those 2^32 addresses would point to?