Improve Article

Save Article

Like Article

Improve Article

Save Article

Like Article

Prerequisite – 8254 Programmable Interval Timer After power-up, the state of the 8254 is undefined. The Mode, count value, and output of all Counters are undefined. How each counter operates is determined when it is programmed. Each counter must be programmed before it can be used. Unused counters need not be programmed. Counters are programmed by writing a Control Word and then an initial count.

Control Word of 8254 – The format of Control Word of 8254 is:

Here by using the value of SC1 and SC0 we select a specific counter:

| SC1 | SC0 | SELECTION |

|---|---|---|

| 0 | 0 | C0 |

| 0 | 1 | C1 |

| 1 | 0 | C2 |

| 1 | 1 | Read back status |

The values of RW1 and RW0 are used to decide the Read – Write operation:

| RW1 | RW0 | SELECTION |

|---|---|---|

| 0 | 0 | Counter Latch Command |

| 0 | 1 | Read/Write lower byte |

| 1 | 0 | Read/Write higher byte |

| 1 | 1 | Read/Write lower byte followed by higher byte |

The values of M2, M1, M0 are used to decide the operating modes of 8254:

| M2 | M1 | M0 | OPERATING MODE |

|---|---|---|---|

| 0 | 0 | 0 | MODE 0 |

| 0 | 0 | 1 | MODE 1 |

| X (0/1) | 1 | 0 | MODE 2 |

| X (0/1) | 1 | 1 | MODE 3 |

| 1 | 0 | 0 | MODE 4 |

| 1 | 0 | 1 | MODE 5 |

The LSB of Control Word is used to select whether the counter is Binary or BCD. If the bit is 0 it works as binary counter and if its value is 1 it works as BCD counter. Operating Modes of 8254:

- Mode 0 (Interrupt on Terminal Count) – Mode 0 is typically used for event counting. After the Control Word is written, OUT is initially low, and will remain low until the counter reaches zero it is decremented by 1 after every clock cycle. OUT then goes high and remains high until a new count or a new Mode 0 Control Word is written into the counter. GATE = 1 enables counting, GATE = 0 disables counting.

- Mode 1 (Hardware Retriggerable One Shot) – OUT will be initially high. OUT will go low on the CLK pulse following a trigger to begin the one-shot pulse, and will remain low until the counter reaches zero.

- Mode 2 (Rate Generator) – Initially value of OUT is low. When counting is enabled, it becomes high and this process repeats periodically. Value of count = Input Frequency / Output Frequency. This mode works as a frequency divider.

- Mode 3 (Square Wave Generator) – Counting is enabled when GATE = 1 and disabled when GATE = 0. This mode is used to generate square waveform and time period (equal to count) is generated. If N is count and is even then ontime of wave = N/2 and offtime = N/2 If N is odd the ontime = (N + 1) / 2 and offtime = (N – 1) / 2

- Mode 4 (Software Triggered Strobe) – In this mode counting is enabled by using GATE = 1 and disabled by GATE = 0. Initially value of OUT is high and becomes low when value of count is at last stage. Count is reloaded again for subsequent clock pulse.

- Mode 5 (Hardware Triggered Strobe) – OUT will initially be high. Counting is triggered by a rising edge of GATE. When the initial count has expired, OUT will go low for one clock pulse and then go high again. After writing the Control Word and initial count, the counter will not be loaded until the clock pulse after a trigger.

Like Article

Save Article

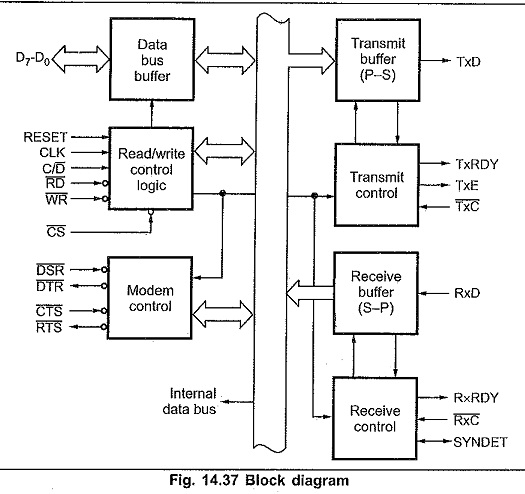

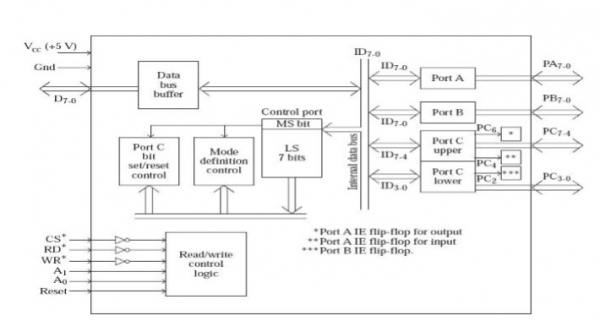

Fig. 14.37 shows the 8251 Block Diagram in Microprocessor. It includes : Data bus buffer, Read/Write control logic, modem control, Transmit buffer, Transmit Control, Receiver Buffer and Receiver control.

Data Bus Buffer :

This tri-state, bi-directional, 8-bit buffer is used to interface 8251 Block Diagram in Microprocessor to the system data bus. Along with the data, control word, command words and status information are also transferred through the Data Bus Buffer.

Read/Write control logic :

This functional block accepts inputs from the system control bus and generates control signals for overall device operation. It decodes control signals on the 8085 control bus into signals which controls the internal and external I/O bus. It contains the control word register and command word register that stores the various control formats for the device functional definition.

Transmit Buffer:

The transmit buffer accepts parallel data from the CPU, adds the appropriate framing information, serializes it, and transmits it on the TxD pin on the falling edge of TxC.

It has two registers : A buffer register to hold eight bits and an output register to convert eight bits into a stream of serial bits. The CPU writes a byte in the buffer register, Which is transferred to the output register when it is empty. The output register then transmits serial data on the TxD pin.

In the asynchronous mode the transmitter always adds START bit; depending on how the unit is programmed, it also adds an optional even or odd parity bit, and either 1, 1 1/2, or 2 STOP bits. In synchronous mode no extra bits (other than parity, if enable) are generated by the transmitter.

8251 Transmitter Control :

It manages all activities associated with the transmission of serial data. It accepts and issues signals both externally and internally to accomplish this function.

TxRDY (Transmit Ready ) : This output signal indicates CPU that buffer register is empty and the USART is ready to accept a data character. It can be used as an interrupt to the system or, for polled operation, the CPU can ‘check TxRDY using the status read operation. This signal is reset when a data byte is loaded into the bliffer register.

TxE (Transmitter Empty) : This is an output signal. A high on this line indicates that the output buffer is empty. In the synchronous mode, if the CPU has failed to load a new character in time, TxE will go high momentarily as SYN characters are loaded into the transmitter to fill the gap in transmission.

TxC (Transmitter Clock) : This clock controls the rate at which characters are transmitted by USART. In the synchronous mode TxC is equivalent to the ‘baud rate, and is supplied by the modem. In asynchronous mode TxC is 1, 16, or 64 times the baud rate. The clock division is programmable. It can be programmed by writing proper mode word in the mode set register.

Receiver Buffer:

The receiver accepts serial data on the RxD line, converts this serial data to parallel format, checks for bits or characters that are unique to the communication technique and sends an “assembled” character to the CPU.

When 8251 Block Diagram in Microprocessor is in the asynchronous mode an4 it is ready to accept a character, it looks for a low level on the RxD line. When it receives the low level, it assumes that it is a START bit and enables an internal counter, At a count equivalent to one-half of a hit time, the RxD line is sampled again. If the line is still low, a valid START bit is detected and the 8251A proceeds to assemble the character. After successful reception of a START bit the 8251A receives data, parity and STOP bits, and then transfers the data on the receiver input register. The data is then transferred into the receiver buffer register.

In the synchronous mode the receiver simply receives the specified number of data bits and transfers them to the receiver input register and then to the receiver buffer register.

Receiver Control:

It manages all receiver-related activities. Along with data reception, it does false start bit detection, parity error detection, framing error detection, sync detection and break detection.

RxRDY (Receiver Ready) : This is an output signal. It goes high (active), when the USART has a character in the buffer register and is ready to transfer it to the CPU. This line can be used either to indicate the status in the status register or to interrupt the CPU. This signal is reset when a data byte from receiver buffer is read by the CPU.

RxC (Receiver Clock) : This clock controls the rate at which the character is to be received by USART in the synchronous mode. RxC is equivalent to the baud rate, and is supplied by the modem. In asynchronous mode RxC is 1, 16, or 64 times the baud rate. The clock division is programmable. It can be programmed by writing proper mode word in the mode set register.

Modem Control:

The 8251 Block Diagram in Microprocessor has a set of control inputs and output’s that can be used to simplify the interface to almost any modem. It provides control circuitry for the generation of RTS and DTR and the reception of CTS and DSR. In addition, a general purpose inverted output and a general purpose input are provided. The output is labeled DTR and the input is labeled DSR. DTR can be asserted by setting bit 2 of the command instruction; DSR can be sensed as bit 7 of the status register. When used as a modem control signal DTR indicates that the terminal is ready to communicate and DSR indicates that it is ready for communication.

Control Word of 8251:

The Control Word of 8251 defines the complete functional definition of 8251 Block Diagram in Microprocessor and they must be loaded before any transmission or reception. The control words of Block Diagram of 8251 Microcontroller are split into two formats

- Mode instruction

- Command instruction

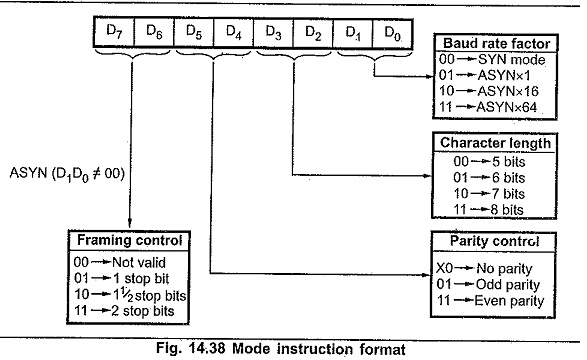

Mode Instruction : Fig. 14.38 shows the mode instruction format of 8251.

The instruction can be considered as four 2-bit fields. The first 2-bit field (D1-D0) determines whether the USART is to operate in the synchronous (00) or asynchronous mode. In the asychronous mode, this field determines the division factor for clock to decide the baud rate. For example, if D1 and D0 are both ones, the RxC and TxC will be divided by 64 to establish the baud rate.

The second 2-bit field (D3-D2) determines number of data bits in one character. With this 2-bit field we can set character length from 5-bits to 8 bits.

The third 2-bit field, (D5-D4), controls the parity generation. The parity bit is added to the data bits only if parity is enabled.

The last field, (D7-D6), has two meanings depending on whether operation is to be in the synchronous or asynchronous mode. For asynchronous mode, (i.e. D1D0 ≠ 00), it controls the number of STOP bits to be transmitted with the character. In synchronous mode, (i.e. D1D0) = 00) this field controls the synchronizing process. It decides whether to operate with external synchronization or internal synchronization and whether to transmit single synchronizing character or two synchronizing characters.

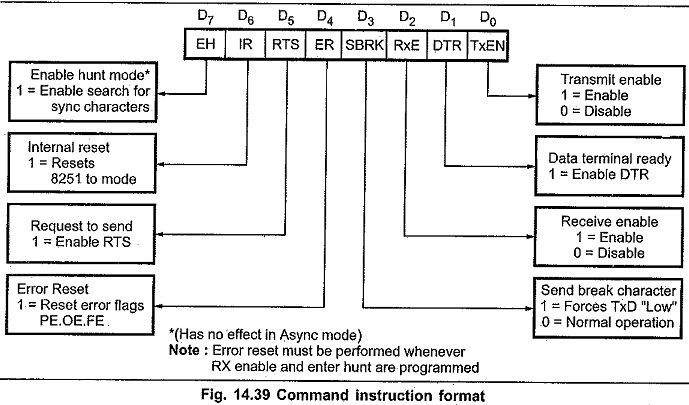

Command Instruction:

After the mode instruction, command character should be issued to the USART. It controls the operation of the USART within the basic frame work established by the mode instruction. Fig. 14.39 shows command instruction format.

It does function such as : Enable Transmit/Receive; Error Reset and modem Control.

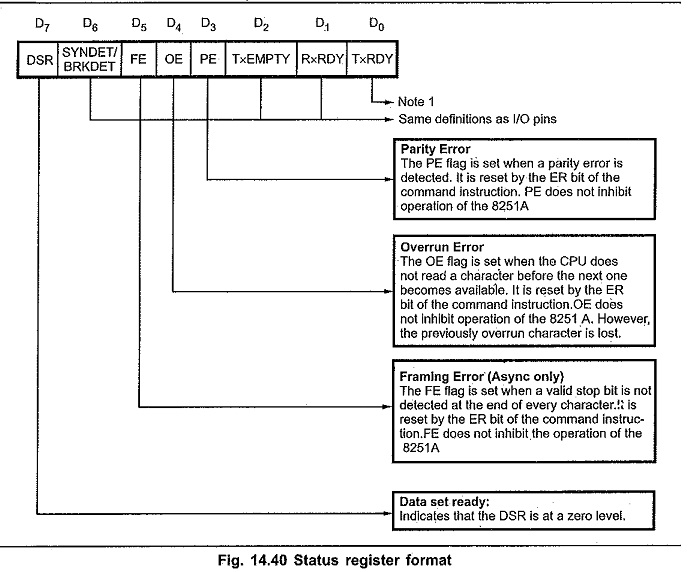

8251A Status Word:

In the data communication systems it is often necessary to examine the “status” of the transmitter and receiver. It is also necessary for CPU to know if any error has occurred during communication. The 8251 Block Diagram in Microprocessor allow the programmer to read above mentioned information from the status register any time during the functional operation. Fig. 14.40 shows the format of status register.

Error Definitions:

Parity Error : At the time of transmission of data an even or odd parity bit is inserted in the data stream. At the receiver end, if parity of the character does not match with the pre-defined parity, parity error occurs.

Overrun Error : In the receiver section received character is stored in the receiver buffer. The CPU is supposed to read this character before reception of the next character. But if CPU fails in reading the character loaded in the receiver buffer, the next the received character replaces the previous one and the OVERRRUN Error occurs.

Framing Error : If valid stop bit is not detected at the end each character framing error occurs.

All these errors, when occur, set the corrosponding bits in the status register. These error bits are reset by setting ER bit in the command instruction.

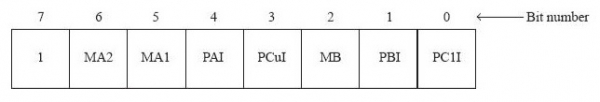

As i mansion my earlier post that is send by programer to make understand 8255 that which port is Input and which one is Output. Now how we are do that ?

Format of Control Word

Mode Definition Control Byte. Indicate by bit b7=1.

Port A and upper half of Port C (Group A)

Bit b3 to bit b6 control the mode and direction of Group A

b6, b5 mode operation

0 0 mode 0

0 1 mode 1

1 0 mode 2

b4 Port A direction, 0=output, 1=input

b3 upper half of Port C direction, 0=output, 1=input

Port B and lower half of Port C (Group B)

Bit b0 to bit b2 control the mode and direction of Group B

b2 mode operation, 0=mod 0, 1=mod 1

b1 Port B direction, 0=output, 1=input

lower half of Port C direction, 0=output, 1=input

Now take a Example that we need Port A as a input Port and Port B as a Out put Port What will be the Control Word ?

For that we need Bit D7 =1 ( For Input/Output Operation )

D6 =0

D5 =0

D4 =1 ( For Port A as Input)

D3 =0

D2 =0

D1 =0 (For Port B as Output)

D0 =0

So finally we got the number 10010000 or 90H.

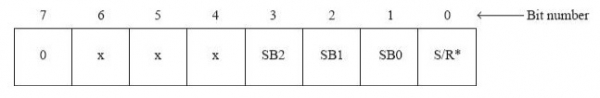

In 8255, there are two types of command words or control word are available. And they are −

-

Mode definition control word and

-

Port C bit set/reset control word.

Both these are written to the control port only. From the point of view of the microprocessor there is a single 8-bit control port, which is selected when CS* = 0, WR* = 0, A1 = 1 and A0 = 1. But if we consider the architecture of 8255, internally there are two control ports, one for mode definition control and another for Port C bit set/reset control. The contents of the control port get latched in mode definition control port if the MS bit of control port = 1. If the MS bit of control port = 0, the contents of the control port gets latched in Port C bit set/reset control port. This can be seen from the following fig.

Now let us discuss about the Mode Definition Control Word. The following fig depicts the same −

The following table depicts the meaning and purposes for all these bits −

| Bit 0 (PClI) | 1 = Port C lower (PC3-0) as input 0 = Port C lower (PC3-0) as output |

| Bit 1 (PBI) | 1 Port B as input 0 = Port B as output |

| Bit 2 (MB) | 1 = Port B in mode 1 0 = Port B in mode 0 |

| Bit 3 (PCuI) | 1 = Port C upper (PC7-4) as input 0 = Port C upper (PC7-4) as output |

| Bit 4 (PAI) | 1 = Port A as input 0 = Port A as output |

| Bits 6, 5 | 0 0 = Port A in mode 0 |

| (MA2,MA1) | 0 1 = Port A in mode 1 1 0 = Port A in mode 2 1 1 = Port A in mode 2 |

| Bit 7 | Must be 1 to indicate that it is mode definition control. |

Now let us discuss about the Port C Bit Set/Reset C4 Word. The following fig depicts the same −

The following table depicts the meaning and purposes for all these bits −

| Bit 0 (S/R*) | 1 = Set Port C bit selected by bits 3, 2, and 1 0 = Reset Port C bit selected by bits 3, 2, and 1 |

| Bits 3, 2, 1 (SB2, 1, 0) | 000 = Select bit 0 of Port C 001 = Select bit 1 of Port C 010 = Select bit 2 of Port C 011 = Select bit 3 of Port C 100 = Select bit 4 of Port C 101 = Select bit 5 of Port C 110 = Select bit 6 of Port C 111 = Select bit 7 of Port C |

| Bits 6, 5, 4 | Are don’t cares. Generally loaded with 000 |

| Bit 7 | 0 to indicate it is Port C bit set/reset control |

Subjects>Electronics>Computers

Wiki User

∙ 15y ago

Want this question answered?

Be notified when an answer is posted

Study guides

Add your answer:

Earn +

20

pts

Q: What are control words in microprocessor?

Write your answer…

Submit

Still have questions?

Related questions

People also asked