From Wikipedia, the free encyclopedia

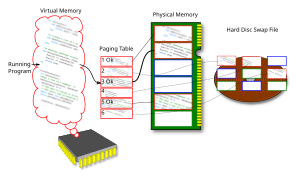

In a computer using virtual memory, accessing the location corresponding to a memory address may involve many levels.

In computing, a memory address is a reference to a specific memory location used at various levels by software and hardware.[1] Memory addresses are fixed-length sequences of digits conventionally displayed and manipulated as unsigned integers. Such numerical semantic bases itself upon features of CPU (such as the instruction pointer and incremental address registers), as well upon use of the memory like an array endorsed by various programming languages.

Types[edit]

Physical addresses[edit]

A digital computer’s main memory consists of many memory locations. Each memory location has a physical address which is a code. The CPU (or other device) can use the code to access the corresponding memory location. Generally only system software, i.e. the BIOS, operating systems, and some specialized utility programs (e.g., memory testers), address physical memory using machine code operands or processor registers, instructing the CPU to direct a hardware device, called the memory controller, to use the memory bus or system bus, or separate control, address and data busses, to execute the program’s commands. The memory controllers’ bus consists of a number of parallel lines, each represented by a binary digit (bit). The width of the bus, and thus the number of addressable storage units, and the number of bits in each unit, varies among computers.

Logical addresses[edit]

A computer program uses memory addresses to execute machine code, and to store and retrieve data. In early computers logical and physical addresses corresponded, but since the introduction of virtual memory most application programs do not have a knowledge of physical addresses. Rather, they address logical addresses, or virtual addresses, using the computer’s memory management unit and operating system memory mapping; see below.

Unit of address resolution[edit]

Most modern computers are byte-addressable. Each address identifies a single byte (eight bits) of storage. Data larger than a single byte may be stored in a sequence of consecutive addresses. There exist word-addressable computers, where the minimal addressable storage unit is exactly the processor’s word. For example, the Data General Nova minicomputer, and the Texas Instruments TMS9900 and National Semiconductor IMP-16 microcomputers used 16 bit words, and there were many 36-bit mainframe computers (e.g., PDP-10) which used 18-bit word addressing, not byte addressing, giving an address space of 218 36-bit words, approximately 1 megabyte of storage. The efficiency of addressing of memory depends on the bit size of the bus used for addresses – the more bits used, the more addresses are available to the computer. For example, an 8-bit-byte-addressable machine with a 20-bit address bus (e.g. Intel 8086) can address 220 (1,048,576) memory locations, or one MiB of memory, while a 32-bit bus (e.g. Intel 80386) addresses 232 (4,294,967,296) locations, or a 4 GiB address space. In contrast, a 36-bit word-addressable machine with an 18-bit address bus addresses only 218 (262,144) 36-bit locations (9,437,184 bits), equivalent to 1,179,648 8-bit bytes, or 1152 KiB, or 1.125 MiB — slightly more than the 8086.

Some older computers (decimal computers), were decimal digit-addressable. For example, each address in the IBM 1620’s magnetic-core memory identified a single six bit binary-coded decimal digit, consisting of a parity bit, flag bit and four numerical bits. The 1620 used 5-digit decimal addresses, so in theory the highest possible address was 99,999. In practice, the CPU supported 20,000 memory locations, and up to two optional external memory units could be added, each supporting 20,000 addresses, for a total of 60,000 (00000–59999).

Word size versus address size[edit]

Word size is a characteristic of computer architecture denoting the number of bits that a CPU can process at one time. Modern processors, including embedded systems, usually have a word size of 8, 16, 24, 32 or 64 bits; most current general-purpose computers use 32 or 64 bits. Many different sizes have been used historically, including 8, 9, 10, 12, 18, 24, 36, 39, 40, 48 and 60 bits.

Very often, when referring to the word size of a modern computer, one is also describing the size of address space on that computer. For instance, a computer said to be «32-bit» also usually allows 32-bit memory addresses; a byte-addressable 32-bit computer can address 232 = 4,294,967,296 bytes of memory, or 4 gibibytes (GiB). This allows one memory address to be efficiently stored in one word.

However, this does not always hold true. Computers can have memory addresses larger or smaller than their word size. For instance, many 8-bit processors, such as the MOS Technology 6502, supported 16-bit addresses— if not, they would have been limited to a mere 256 bytes of memory addressing. The 16-bit Intel 8088 and Intel 8086 supported 20-bit addressing via segmentation, allowing them to access 1 MiB rather than 64 KiB of memory. All Intel Pentium processors since the Pentium Pro include Physical Address Extensions (PAE) which support mapping 36-bit physical addresses to 32-bit virtual addresses. Many early processors held 2 addresses per word , such as 36-bit processors.

In theory, modern byte-addressable 64-bit computers can address 264 bytes (16 exbibytes), but in practice the amount of memory is limited by the CPU, the memory controller, or the printed circuit board design (e.g., number of physical memory connectors or amount of soldered-on memory).

Contents of each memory location[edit]

Each memory location in a stored-program computer holds a binary number or decimal number of some sort. Its interpretation, as data of some data type or as an instruction, and use are determined by the instructions which retrieve and manipulate it.

Some early programmers combined instructions and data in words as a way to save memory, when it was expensive: The Manchester Mark 1 had space in its 40-bit words to store little bits of data – its processor ignored a small section in the middle of a word – and that was often exploited as extra data storage.[citation needed] Self-replicating programs such as viruses treat themselves sometimes as data and sometimes as instructions. Self-modifying code is generally deprecated nowadays, as it makes testing and maintenance disproportionally difficult to the saving of a few bytes, and can also give incorrect results because of the compiler or processor’s assumptions about the machine’s state, but is still sometimes used deliberately, with great care.

Address space in application programming[edit]

In modern multitasking environment, an application process usually has in its address space (or spaces) chunks of memory of following types:

- Machine code, including:

- program’s own code (historically known as code segment or text segment);

- shared libraries.

- Data, including:

- initialized data (data segment);

- uninitialized (but allocated) variables;

- run-time stack;

- heap;

- shared memory and memory mapped files.

Some parts of address space may be not mapped at all.

Some systems have a «split» memory architecture where machine code, constants, and data are in different locations, and may have different address sizes.

For example, PIC18 microcontrollers have a 21-bit program counter to address machine code and constants in Flash memory, and 12-bit address registers to address data in SRAM.

Addressing schemes[edit]

A computer program can access an address given explicitly – in low-level programming this is usually called an absolute address, or sometimes a specific address, and is known as pointer data type in higher-level languages. But a program can also use relative address which specifies a location in relation to somewhere else (the base address). There are many more indirect addressing modes.

Mapping logical addresses to physical and virtual memory also adds several levels of indirection; see below.

Memory models[edit]

Many programmers prefer to address memory such that there is no distinction between code space and data space (see above), as well as from physical and virtual memory (see above) — in other words, numerically identical pointers refer to exactly the same byte of RAM.

However, many early computers did not support such a flat memory model — in particular, Harvard architecture machines force program storage to be completely separate from data storage.

Many modern DSPs (such as the Motorola 56000) have three separate storage areas — program storage, coefficient storage, and data storage. Some commonly used instructions fetch from all three areas simultaneously — fewer storage areas (even if there were the same total bytes of storage) would make those instructions run slower.

Memory models in x86 architecture[edit]

Early x86 processors use the segmented memory model addresses based on a combination of two numbers: a memory segment, and an offset within that segment.

Some segments are implicitly treated as code segments, dedicated for instructions, stack segments, or normal data segments. Although the usages are different, the segments do not have different memory protections reflecting this.

In the flat memory model all segments (segment registers) are generally set to zero, and only offsets are variable.

See also[edit]

- Base address

- Endianness

- Low-level programming language

- Memory address register

- Memory allocation

- Memory management unit (MMU)

- Memory model (programming)

- Memory protection

- Memory segmentation

- Offset (computer science), also known as a displacement

- Page table

References[edit]

- ^ Abrahamson, Karl R. (Aug 20, 2022). «5.10.1. The Memory and Memory Addresses». East Carolina University. Retrieved Feb 3, 2023.

{{cite web}}: CS1 maint: url-status (link)

Improve Article

Save Article

Like Article

Improve Article

Save Article

Like Article

Memory is a storage component in the Computer used to store application programs. The Memory Chip is divided into equal parts called as “CELLS”. Each Cell is uniquely identified by a binary number called as “ADDRESS”. For example, the Memory Chip configuration is represented as ’64 K x 8′ as shown in the figure below.

The following information can be obtained from the memory chip representation shown above:

1. Data Space in the Chip = 64K X 8

2. Data Space in the Cell = 8 bits

3. Address Space in the Chip = log_{2} (64 K) =16 bits

Now we can clearly state the difference between Byte Addressable Memory & Word Addressable Memory.

| S. No. | Byte Addressable Memory | Word Addressable Memory |

|---|---|---|

| 1. | When the data space in the cell = 8 bits then the corresponding address space is called as Byte Address. | When the data space in the cell = word length of CPU then the corresponding address space is called as Word Address. |

| 2. | Based on this data storage i.e. Bytewise storage, the memory chip configuration is named as Byte Addressable Memory. | Based on this data storage i.e. Wordwise storage, the memory chip configuration is named as Word Addressable Memory. |

| 3. | For eg. : 64K X 8 chip has 16 bit Address and cell size = 8 bits (1 Byte) which means that in this chip, data is stored byte by byte. | For eg. : For a 16-bit CPU, 64K X 16 chip has 16 bit Address & cell size = 16 bits (Word Length of CPU) which means that in this chip, data is stored word by word. |

| 4. | It is suitable for the processes that require data comprising single byte at a time. A single address is issued for accessing a single byte in byte addressable memory. | In case of word addressable memory, the necessary condition involves computing the address of word that contains required byte, fetch that word and then extraction of needed byte from the two byte word takes place. So, it is indirectly accessible. Hence, modern machines are byte addressable. |

NOTE :

i) The most important point to be noted is that in case of either of Byte Address or Word Address, the address size can be any number of bits (depends on the number of cells in the chip) but the cell size differs in each case.

ii)The default memory configuration in the Computer design is Byte Addressable .

Like Article

Save Article

Memory locations and addresses determine how the computer’s memory is organized so that the user can efficiently store or retrieve information from the computer. The computer’s memory is made of a silicon chip which has millions of storage cell, where each storage cell is capable to store a bit of information which value is either 0 or 1.

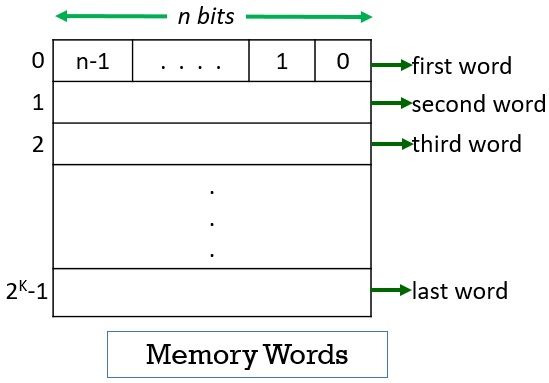

But the fact is, computer memory holds instructions and data. And a single bit is very small to hold this information so bits are rarely used individually. As a solution to this, the bits are grouped in fixed sizes of n bits. The memory of the computer is organized in such a way that the group of these n bits can be stored and retrieved easily by the computer in a single operation.

The group of n bit is termed as word where n is termed as the word length. The word length of the computer has evolved from 8, 16, 24, 32 to 64 bits. General-purpose computers nowadays have 32 to 64 bits. The group of 8 bit is called a byte.

Now, whenever you want to store any instruction or data may it be of a byte or a word you have to access a memory location. To access the memory location either you must know the memory location by its unique name or it is required to provide a unique address to each memory location.

The memory locations are addressed from 0 to 2K-1 i.e. a memory has 2K addressable locations. And thus the address space of the computer has 2K addresses. Let us try some suitable values for K.

210 = 1024 = 1K (Kilobyte)

220 = 1,048,576 = 1M (Megabyte)

230 = 1073741824 = 1G (Gigabyte)

240 = 1.0995116e+12 = 1T (Terabyte)

Byte Addressability

Till now we have gone through three information storing quantities bit, byte and word. We have seen above that 8 bits together form a byte and this is the fix for every memory. But the word length varies from memory to memory and it ranges from 16 to 64 bit.

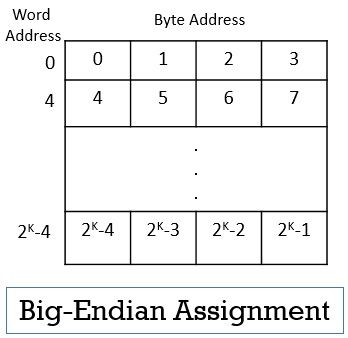

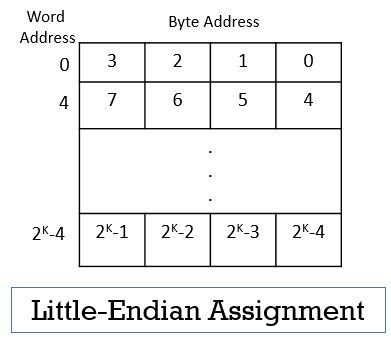

Well, it is impossible to allot a unique address to each bit in memory. As a solution, most modern computers assign successive addresses to successive byte locations in memory. This assignment of addresses to individual byte locations is termed byte addressability and memory is referred to as byte-addressable memory.

If we assign an address to individual byte locations in the memory like 0, 1, 2, 3…. .Now if the word length of the machine is 16 bit then the successive words are located at addresses 0, 2, 4, 6… where each word would have 2 bytes of information. Similarly, if we have a machine with a word length of 32 bit then the successive words are located at the addresses 0, 4, 8, 12… where each word would have 4 bytes of information and it could store or retrieve 4 bytes of instruction or data in a single and basic operation.

Big-Endian and Little-Endian Assignments in Byte Addresses

The big-endian and little-endian are two methods of assigning byte addresses across the words in the memory. In the big-endian assignment, the lower byte addresses are used for the leftmost bytes of the word. Observe the word 0 in the image below, the leftmost bytes of the word have lower byte addresses.

In the little-endian assignment, the lower byte addresses are used for the rightmost bytes of the word. Observe the word 0 in the image below the rightmost bytes of word 0 has lower byte addresses.

The leftmost bytes of the word are termed as most significant bytes and the rightmost bytes of the words are termed as least significant bytes.

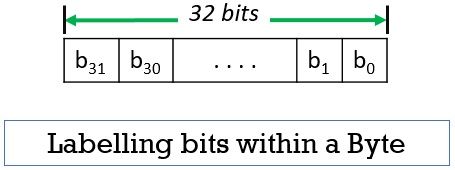

Thus the big-endian and little-endian specify the ordering of bytes inside a word. Similarly, the bits must be labelled inside the byte or a word and the most common way of labelling bits in a byte or word is as shown in the figure below i.e. labelling the bits as b7, b6,…….,b1, b0 from left to write as we do in little-endian assignment.

Word Alignment

In a machine with word length 32-bit, the word boundaries occur at the bytes addresses 0, 4, 8… It is said that the word has aligned addresses if they begin with the byte address that is multiple of the number of bytes present in that word. For example, the word address 4 has four bytes in it with byte address 4, 5 and 6. The word address 4 starts with the byte address 4 which is multiple of the number of bytes in word 4.

In case if the word address begins with the arbitrary byte address the word is said to have unaligned addresses. But conventionally the words have aligned addresses as this lets the access of memory operand more efficiently.

So, this is all about the memory locations and how they are addressed to store and retrieve the instructions or data more efficiently. With memory addresses, it becomes easy to identify a specific memory location.

- A byte is a memory unit for storage

- A memory chip is full of such bytes.

Memory units are addressable. That is the only way we can use memory.

In reality, memory is only byte addressable. It means:

- A binary address always points to

a singlebyte only. - A word is just

a group ofbytes –2,4,8depending upon the data bussize ofthe CPU.

To understand the memory operation fully, you must be familiar with the various registers of the CPU and the memory ports of the RAM. I assume you know their meaning:

- MAR(memory address register)

- MDR(memory data register)

- PC(program counter register)

- MBR(memory buffer register)

RAM has two kinds of memory ports:

32-bitsfor data/addresses8-bitfor OPCODE.

Suppose CPU wants to read a word (say 4 bytes) from the address xyz onwards. CPU would put the address on the MAR, sends a memory read signal to the memory controller chip. On receiving the address and read signal, memory controller would connect the data bus to 32-bit port and 4 bytes starting from the address xyz would flow out of the port to the MDR.

If the CPU wants to fetch the next instruction, it would put the address onto the PC register and sends a fetch signal to the memory controller. On receiving the address and fetch signal, memory controller would connect the data bus to 8-bit port and a single byte long opcode located at the address received would flow out of the RAM into the CPU‘s MDR.

So that is what it means when we say a certain register is memory addressable or byte addressable. Now what will happen when you put, say decimal 2 in binary on the MAR with an intention to read the word 2, not (byte no 2)?

Word no 2 means bytes 4, 5, 6, 7 for 32-bit machine. In real physical memory is byte addressable only. So there is a trick to handle word addressing.

When MAR is placed on the address bus, its 32-bits do not map onto the 32 address lines(0-31 respectively). Instead, MAR bit 0 is wired to address bus line 2, MAR bit 1 is wired to address bus line 3 and so on. The upper 2 bits of MAR are discarded since they are only needed for word addresses above 2^32 none of which are legal for our 32 bit machine.

Using this mapping, when MAR is 1, address 4 is put on the bus, when MAR is 2, address 8 is put on the bus and so forth.

It is a bit difficult in the beginning to understand. I learnt it from Andrew Tanenbaums‘s structured computer organisation.

Memory plays a vital role in any computer system and it is very important to understand how it works and how it stores the data. In general, we know that computer memory stores the data after converting into bits or bytes (which is nothing but collection of bits). In this article, we are going to explain how this storage take place and how to address those storage blocks.

Data, or in simple language, every word that we provide to a computer system is being stored in a memory, whether in temporary cache or permanent memory. But before storing it to memory, there is conversion of word into bits. Now the collection of these bits is going to be stored in the memory. The memory of a computer system is divided into chunks or we can say «sections» which basically hold the converted bits.

What is Word Addressable Memory?

Let us take an example. Suppose your computer memory configuration is 4096 * 32 bit which means that it has 4096 locations or sections and each of these sections can hold a word of size 32 bits. And let us suppose the address of the first section among 4096 sections is ‘i’, then the address of its subsequent section would be ‘i+1’ and of next is ‘i+3’, and so on. This type of addressing in which we treat each section of memory which is that storage of 32 bits or 4 bytes is known as Word Addressable Memory.

What is Byte Addressable Memory?

Continuing with the same example, we have a total of 4096 sections and each section stores a word of length 32 bits or simply 4 bytes. We can access each of these sections by adding one consecutive number to its current location, i.e., ‘i’, then next location is ‘i+1’, then ‘i+2’, and so on.

If the memory section which is storing the words is further treated as subsections of 4, i.e., as each section which is storing a word of 4 byte is divided in 4 subsection and each subsection is storing 1 byte.

Let us suppose that each subsection has an address, now each subsection has address like ‘j’ next would be ‘j+1’ then ‘j+3’ and so on. If we take the address of one section as ‘j’, then the address of the next section would be ‘j+4’, then for the next would be ‘j+8’, and so on.

This type of addressing in which the number of subsections, i.e., number of bytes stored in a section is added to get the address of the next section is known as Byte Addressable Memory.

If we take ‘i’ address in Word Addressable memory and ‘j’ in Byte Addressable memory address, then ‘i’ = ‘j’ ; ‘i=1’ = ‘j+4’ ; ‘i=3’ = ‘j+8’, and so on.

Difference between Byte Addressable Memory and Word Addressable Memory

The following are the important differences between byte addressable memory and word addressable memory −

|

S.No. |

Byte Addressable Memory |

Word Addressable Memory |

|---|---|---|

|

1. |

Byte addressable memory is one in which the data space in a cell is equal to 8 bits or 1 byte. |

Word addressable memory is one in which the data space in a cell is equal to the word length of the CPU. |

|

2. |

It is called byte addressable memory because it uses bytewise storage configuration. |

It is called word addressable memory because it uses wordwise storage configuration. |

|

3. |

Byte addressable memory is best suited for the processes that need a single byte data at a time. |

Word addressable memory is suitable for processes that requires data comprising single word at a time. |

|

4. |

The byte addressable memory issues a single address for accessing a single byte. |

The word accessible memory issues the address of word that contains required byte. |

|

5. |

Byte addressable memory is a default memory configuration in computer design. |

Word addressable memory is not a default configuration. |

|

6. |

A memory chip with 64K × 8 has 16 bit address and cell size equal to 8 bits, i.e. 1 byte. |

For a 16-bit processor, a memory chip with 64K × 16 has 16 bit address and cell size equal to 16 bits, i.e. word length of processor. |

|

7. |

Byte addressable memory chip stores data byte by byte. |

Word addressable memory chip stores data word by word. |

Conclusion

Both Byte addressable memory and Word addressable memory have address size that can be of any number of bits depending upon the number of cells in memory chip. But, the cell size is different in each case.

The most significant difference that you should note here is that byte addressable memory uses bytewise data storage, whereas word addressable memory uses wordwise data storage.